# 5G Beamforming with Versal Al Core Series

- > 2X TMACs/watt1

- > Support for adaptable O-RAN O-DU and O-RU functional partitioning

- > Adaptable beamforming for evolving algorithms

# **CHALLENGE**

5G New Radio (NR) beamforming is the key to enabling a dramatic increase in network capacity. Beamforming technology, however, requires significant compute density and advanced high-speed connectivity to meet 5G throughput and low-latency requirements. The massive MIMO beamforming algorithms are expected to continue to evolve to increase the utilization of inherent network capacity possible within massive MIMO systems while optimizing fronthaul bandwidth and lowering dissipated power in the radio.

Massive MIMO radio is the leading form factor for 5G commercial deployments, using 32 or 64 antenna elements for beamforming steered towards one or multiple users while using the same spectral resources. For typical radio configuration of a 64 antenna 200MHz system, the beamforming device in the radio needs to perform over 1.5 tera multiply and add (TMAC) operations per second for downlink. Additional compute is needed to perform beamforming in the uplink direction, all while meeting stringent thermal and system footprint constraints.

# SOLUTION: VERSAL AI CORE ACAP FOR BEAMFORMING

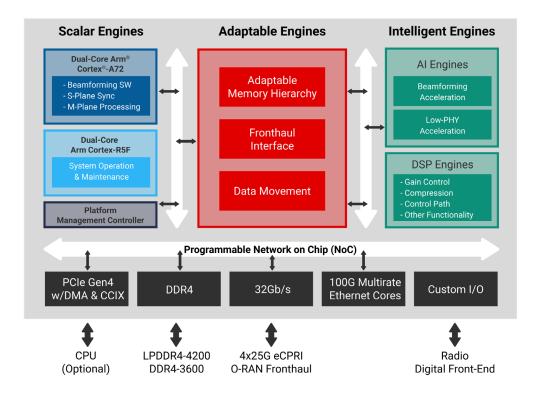

The Versal® Al Core adaptive compute acceleration platform (ACAP) is a highly integrated, multicore, heterogeneous platform that delivers exceptional compute density at low power consumption to perform the real-time, low-latency signal processing demanded by beamforming algorithms in massive MIMO radios. Central to the platform are the Al Engines—a tiled array of C-programmable vector processors with flexible interconnect and distributed memory—ideal for implementing beamforming algorithms that can easily be reprogrammed after deployment.

#### Al Engines for Performance/Watt

Al Engines provide system-level compute far beyond that of traditional FPGA-based multipliers and DSP blocks, enabling 2X TMACs/watt<sup>1</sup>, allowing more programmable logic resources to be used for additional functionality.

#### Adaptable O-RAN

By using Versal AI Core ACAPs in conjunction with other Xilinx adaptable solutions, network suppliers and OEMs can split baseband processing across distributed units (DU) and radio units (RU) to realize fully adaptable networks.

#### Adaptable Beamforming

With 5G specifications in flux and beamforming techniques evolving, Versal Al Core ACAPs offer adaptive compute for different algorithm implementations to address a wide range of processing performance and compute precision.

1: Versal Al Core VC1902 ACAP vs. Intel Agilex AGF027 FPGA

# VERSAL ACAP IMPLEMENTATION

#### 64TRX 200MHz+ Massive MIMO Beamformer Device

An ACAP implementation provides software programmability for C/C++ developers, hardware adaptability to evolve with beamforming algorithms, and hard IP integration for the on- and off-chip performance/watt and low latency required for 5G.

| PLATFORM HIGHLIGHTS             |                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al Engines                      | <ul> <li>Tiled array of vector processors capable of fixed- and floating-point signal processing and massive parallelism</li> <li>Perform on-the-fly calculation of phase and gain coefficients for beamforming and Low-PHY acceleration</li> <li>C/C++ programmable with 1GHz performance</li> </ul>                                           |

| Adaptable Engines               | <ul> <li>Manage ingress and egress data movement, dynamically controlling accelerators based on radio configuration</li> <li>Fine grained memory hierarchy to optimize accelerator performance</li> <li>Fronthaul interface logic—including eCPRI &amp; 1588-PTP packet filter &amp; framer/de-framer, xRAN pre-processing, and more</li> </ul> |

| Scalar Engines                  | <ul> <li>Manage initial system configuration and run-time control</li> <li>Perform system operation and maintenance (OA&amp;M), S-Plane sync, and M-Plane processing</li> <li>Run beamforming application software</li> </ul>                                                                                                                   |

| Programmable<br>Network on Chip | <ul> <li>Seamlessly integrates all engines and key interfaces</li> <li>Simplifies kernel and IP placement, reducing soft logic needed for connectivity</li> <li>Streamlines programming experience for software and hardware developers</li> </ul>                                                                                              |

| Integrated Shell                | <ul> <li>Comprises hardened interface (PCIe® w/DMA, DDR4 controllers) and programmable network on chip (NoC)</li> <li>Ensures streamlined device bring-up and connectivity to off-chip interfaces-making the platform available at boot</li> <li>Delivers pre-engineered timing closure and logic resource savings</li> </ul>                   |

| Multirate 100G<br>Ethernet      | <ul> <li>Enables 10G/25G/50G eCPRI over Ethernet</li> <li>Optional built-in RS-FEC / FEC and IEEE Std 1588 hardware timestamping</li> </ul>                                                                                                                                                                                                     |

# **BENCHMARK**

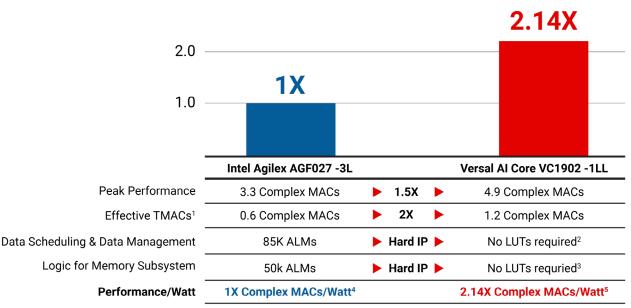

Shown below is a comparison of projected results for a 7nm production Versal VC1902 device vs. a 10nm Intel Agilex FPGA. Xilinx Versal Al Engine technology increases desired compute density while reducing power in contrast to an Agilex AGF027 based on traditional FPGA fabric, multipliers, memory, and soft interconnect.

#### 64TRX 200MHz+ Massive MIMO Beamformer Device

- 1: Assumes 75% DSP utilization for 17.056 Intel Agilex FPGA 18x19 multipliers and 300 of 400 available Versal ACAP AI Engines

- 2: Versal ACAP AI Engines and AI Engine Interconnect provide data movement for compute

- 3: Versal ACAP hardened memory subsystem comprises network on chip and DDR controllers no programmable logic required

- 4: Based on Quartus Power & Thermal Calculator 2021.2, assumes SmartVID and claimed static power savings

- 5: Based on Xilinx Power Estimator (XPE) available at https://www.xilinx.com/products/technology/power/xpe.html

# TAKE THE NEXT STEP

- > To learn more about beamforming with AI Engines, read the application note or watch the video

- > To try the above benchmark yourself, visit www.xilinx.com/versal-performance-elevated

- > For more information on the Versal Al Core series, visit www.xilinx.com/versal-ai-core

- > To contact your local Xilinx sales representative, visit Contact Sales

Versal AI Core ACAP VCK190 **Evaluation Kit** www.xilinx.com/vck190

Corporate Headquarters

2100 Logic Drive San Jose, CA 95124 Tel: 408-559-7778

www.xilinx.com

Xilinx Europe Xilinx Europe Bianconi Avenue Citywest Business Campus Saggart, County Dublin Ireland Tel: +353-1-464-0311

Japan

Xilinx K.K. Art Village Osaki Central Tower 4F 1-2-2 Osaki, Shinagawa-ku Tokyo 141-0032 Japan Tel: +81-3-6744-7777 japan.xilinx.com

Asia Pacific Pte. Ltd.

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com

Xilinx India Technology Services Pvt. Ltd. Block A, B, C, 8th & 13th floors, Meenakshi Tech Park, Survey No. 39 Gachibowli(V), Seri Lingampally (M), Hyderabad -500 084 Tél: +91-40-6721-4747 www xilinx com

© Copyright 2021 Advanced Micro Devices, Inc. All rights reserved. Xilinx, the Xilinx logo, AMD, the AMD Arrow logo, Alveo, Artix, Kintex, Kria, Spartan, Versal, Vitis, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight, Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCle, and PCl Express are trademarks of PCl-SIG and used under license. Printed in the U.S.A. AC11-2-21