## Design Closure: Power Constraints, best practices for an accurate Report Power estimation

Feb 2021

### **Design Closure Sessions**

#### Session 1

Methodology, tips, and tricks for achieving better Quality-of-Results

#### Session 2

Using Timing Closure Assistance tools to address tough timing issues

#### Session 3

Power Constraints, best practices for an accurate Report Power estimation

### Agenda

- Power impact and Time to Market

- Design Closure an efficient approach

- Understanding design power

- Design Power Constraints

- Vivado Commands

## **Power impact and Time to Market**

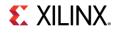

### Why is Power Closure so important?

- Board Design is Fixed

- Power and Thermal Issues take a long time to correct

- Design Changes (Typically Weeks)

- Re-Run P&R

- HDL Changes

- Reducing design specifications

- Hardware changes (Typically Months)

- Board Re-spin

- Power Delivery Changes

- Thermal Solution Changes

### **Power / Thermal / Board Design Methodology**

## **Design Closure an efficient approach**

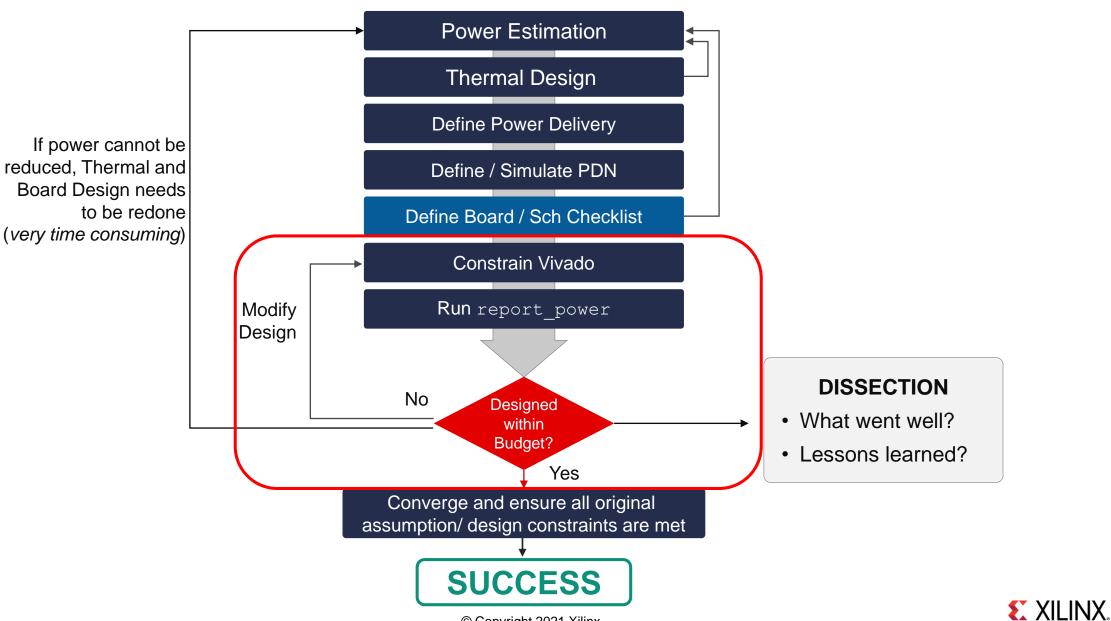

### **Design closure – combining Timing and Power**

More efficient, build a complete picture of timing AND power

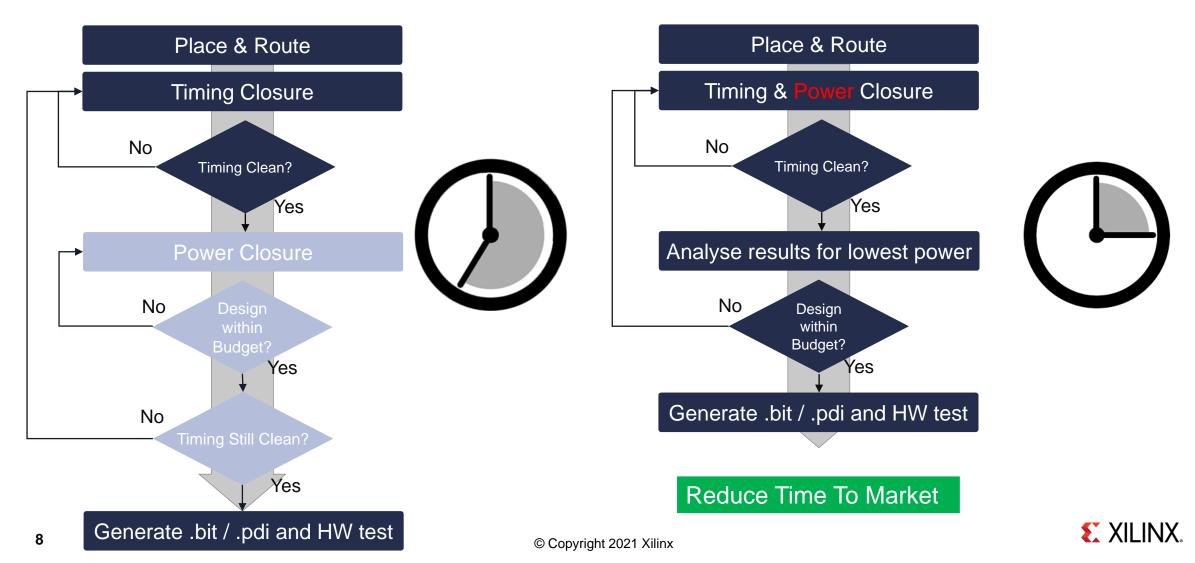

# **Combining Timing and Power gives much more information**

Allows users to take the best run from a Timing AND power perspective, not just the best timing run

Power / Timing Slack for Different P&R Runs

## Understanding design power

### **Design Power – Sum of two Parts**

Dynamic power directly related to the user design

- Resource count, Fmax, toggle rates

- Static Power Junction temperature related

- Rises as Junction temperature rises

- Xilinx provides Typical and Maximum process numbers

- Maximum process should be used for worst case power

- Static power often overlooked

- Causes Power Analysis inaccuracies

- Static power reduction via:

- Thermal solution improvements

- Low Voltage devices

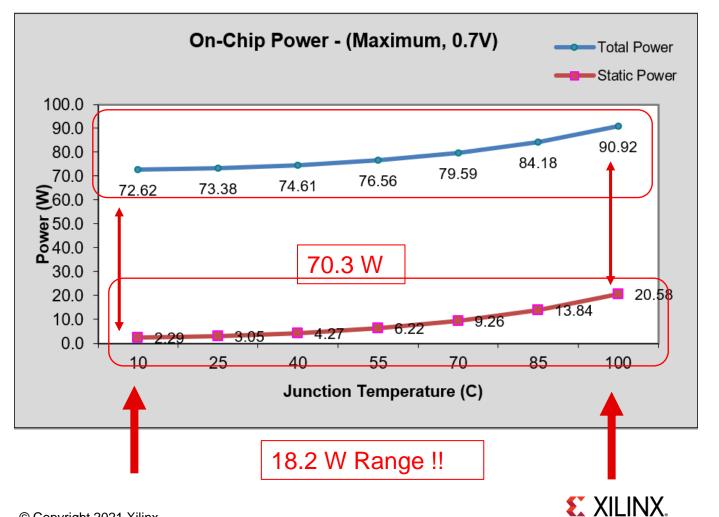

### **Design Power – Sum of Two Parts**

Example of Total Design power over temperature

- Total Power Range 72 90W

- Dynamic power 70.3W

- ► Static power range 2.2 20.5W

▶ 18.2W range

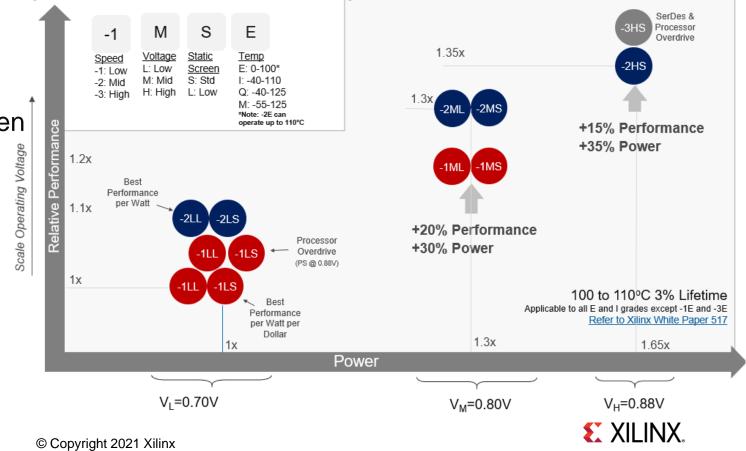

### **Device Selection – impact on Static power**

#### Best Practice is to design for low voltage devices

- Easier to move up if timing is challenged

- Harder to move from High or Mid voltage to Low if power is too high

#### Versal has 3 Voltages

- Low, Mid and High

- Also, Low and Standard Static Screen

- UltraScale Plus

- Supports for Vlow (0.72v)

## **Design Power Constraints**

### Minimum recommended power constraints

- Ensure a power budget is defined

- Maximum process is set

- Without thermal information the MAX Junction Temp (Tj) should be used

- set\_operating\_conditions -design\_power\_budget <Power in Watts>

- set\_operating\_conditions -process maximum

- set\_operating\_conditions -junction\_temp <Max Tj based on Temp Grade>

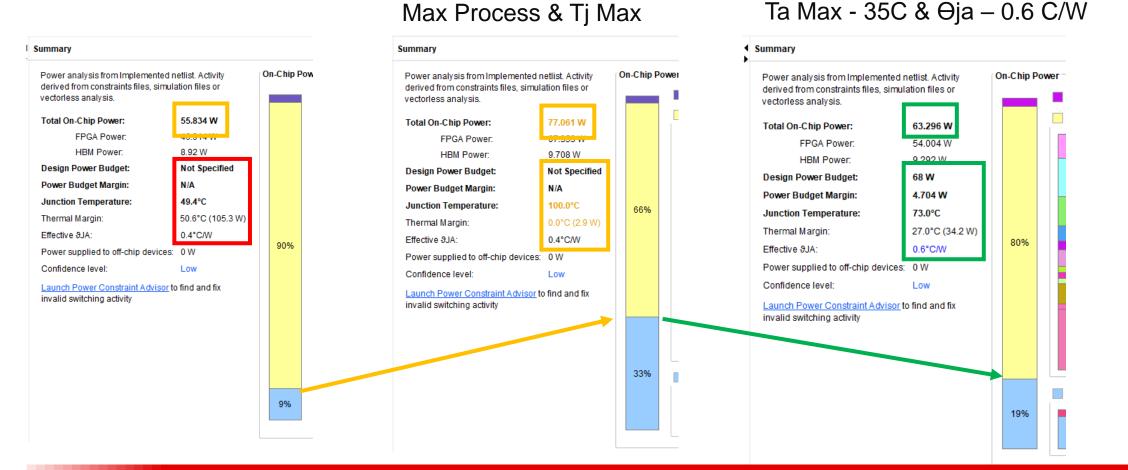

### **Best accuracy Power Constraints**

- Minimum constraints use the Max junction temp

- Worst case Power analysis

- Power Estimate can be refined further

- Defined maximum ambient the application will support

- Define Theta Ja Thermal solution efficiency (C/W)

- For example: 1.5 C/W for every W dissipated Tj increases by 1.5C

set\_operating\_conditions -ambient\_temp <Max Supported by Application>

set\_operating\_conditions -thetaja <Increase in Tj for every W dissipated C/W>

### **Refining Power Estimation using Ta and OJa**

2. Worst Case – 77W

#### 1. No Constraints - 55W

3. Refined -63W

#### **Ensures accurate modelling of Static and Total Power**

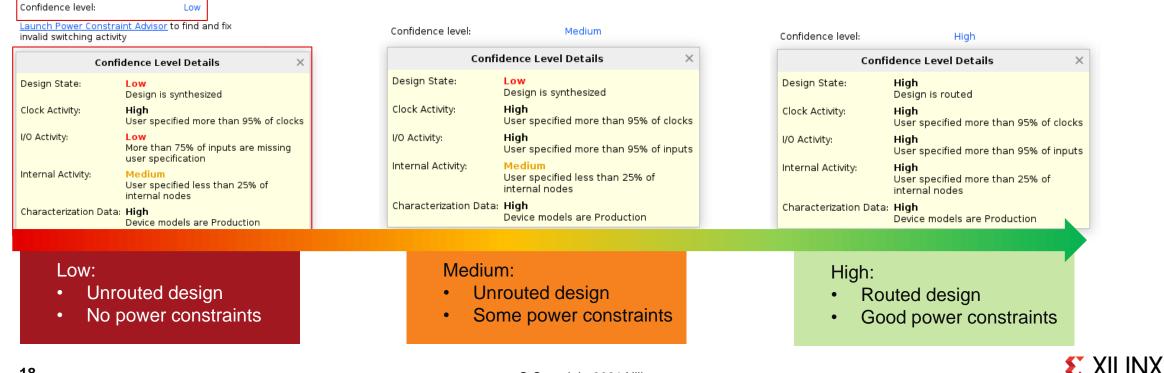

### **Improving the Confidence Level**

Try to achieve High Confidence Level of accuracy - review power reports

- Review switching activity constraints: specify missing and correct invalid constraints

- Report the power after Implementation for accurate signal power

- Use most recent Vivado version for most up-to-date power characterization data

#### **Power Constraints Advisor**

Available from the Launch Power Constraints Advisor in Power Summary

- Simple GUI that shows confidence level of Sets / Resets and Enables

- Allows sorting and filtering

- Start with Low Confidence High Fanout nets

#### Negative power margin clearly shown

| y (70.031 W, Margin: -0.031 W) | Power analysis from Implemented netlist. Activity<br>derived from constraints files, simulation files or<br>vectorless analysis. |                      |   | Net                                      | Confidence 1 | Fanout | Fanout Types              | Polarity    | Static Probability | Toggle Rate % |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------|---|------------------------------------------|--------------|--------|---------------------------|-------------|--------------------|---------------|

| upply                          |                                                                                                                                  |                      |   | Not                                      | Commutence   | ranout | Tanout Types              | rolanty     | [0.0 - 1.0]        | [0 - 100]     |

| Details                        | <b>T</b> ( ) <b>D</b>                                                                                                            | 70.004.00            |   | <pre>_ pfm_top_i/dynact_aresetn[0]</pre> | Low          | 1010   | Set, Reset, Clear, Preset | Both        | 0.573              | 0.667         |

|                                | Total On-Chip Power:                                                                                                             | 70.031 W             |   | _ pfm_top_i/staclp_mem_we[2]             | Low          | 522    | Reg Enable                | Active High | 0.004              | 0.787         |

|                                | FPGA Power:                                                                                                                      | 60.529 W             |   | _ pfm_top_i/dynainst/r_shelf             | Low          | 514    | Reg Enable                | Active High | 0.03               | 5.837         |

|                                | HBM Power:                                                                                                                       | 9.502 W              |   | _ pfm_top_i/dynaias_rvalid[0]            | Low          | 512    | Reg Enable                | Active High | 0.013              | 1.518         |

|                                | Design Power Budget:                                                                                                             | 70 W                 |   | _ pfm_top_i/dynat_reg[0]_0[0]            | Low          | 512    | Reg Enable                | Active High | 0.001              | 0.081         |

|                                | Power Budget Margin:                                                                                                             | -0.031 W             |   | _ pfm_top_i/dynat_reg[0]_0[0]            | Low          |        | Reg Enable                | Active High | 0.001              | 0.08          |

|                                | Junction Temperature:                                                                                                            | 91.0°C               | n |                                          | Low          |        | Reg Enable                | Active High | 0.001              | 0.082         |

|                                | Thermal Margin:                                                                                                                  | 9.0°C (7.1 W)        |   | pfm_top_i/dynat_reg[0]_0[0]              | Low          |        | Reg Enable                | Active High | 0.001              | 0.084         |

|                                | Effective &JA:                                                                                                                   | 0.8°C/W              |   | _ pfm_top_i/dynaata_reg[29][0]           |              |        | Reg Enable                | Active High | 0.001              | 0.098         |

|                                | Power supplied to off-chip dev                                                                                                   | rices: 0 W           |   | onstraints will be applied               |              |        |                           |             |                    |               |

|                                | Confidence level.                                                                                                                | Lon                  |   |                                          |              |        |                           |             |                    |               |

|                                | Launch Power Constraint Adv                                                                                                      | isor to find and fix | ? |                                          |              |        |                           |             | (                  | ок Са         |

ive periods of time. Review this table and modif

Switching Activity for Review and Correcti

The Power Constraint Advisor will check the design for abnormal switching activity on control signals such as inactive enables and set/reset signals that are asserted fo

inaccurate switching activity on critical control signals. Reasonable switching activity ensures the most accurate

Power Constraints Adviso

nower measurements

### **Power Rail Constraints**

- New Feature in Vivado 2020.2

- Should be used in addition to Design Power Budget

- Allows regulator power to be validated

- Create a new power rail:

- create\_power\_rail <power rail name> -power\_sources {supply1, supply2 ,..}

#### Add power sources to an existing power rail.

- add\_to\_power\_rail <power rail name> -power\_sources {supply1, supply2, ..}

#### Define current budget:

set\_operating\_conditions -supply\_current\_budget {<supply rail name> <current budget in Amp>} -voltage {<supply rail name> <voltage>}

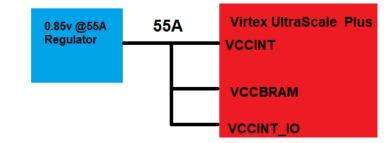

### **Power Rail Constraints – Example**

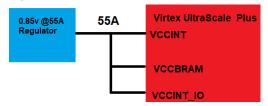

Direct: Single regulator to 1 or more rails

create\_power\_rail board\_85V -power\_sources {VCCINT VCCBRAM VCCINT\_IO}

set\_operating\_conditions -supply\_current\_budget {board\_85V 55} -voltage {board\_85V 0.85}

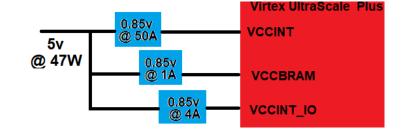

- Indirect: Two or more regulator stages

- Can define multiple regulation stages

- Example: Board supply power and Rail current

Set\_operating\_conditions -supply\_current\_budget {VCCINT 50 VCCBRAM 1 VCCINT\_IO 4}

S XII INX

21

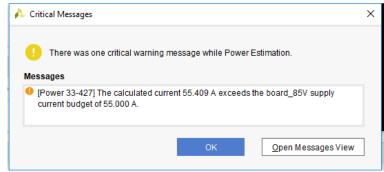

### **Power Rail Constraints - Results**

#### Single regulator to 1 or more rails

#### Critical Warning Generated

#### Margin Reported in Text report:

| Source                | Voltage (V) | Total (A)          | Budget (A)   Margin (A)                |

|-----------------------|-------------|--------------------|----------------------------------------|

| board_85V<br>  Vccint | 0.850       | 55.409  <br>47.652 | 55.000   -0.409 (VIOLATED)             |

| Vccbram<br>Vccint io  | 0.850       | 0.644              | Unspecified   NA  <br>Unspecified   NA |

| Vccaux                | 1.800       | 1.420*             | Unspecified   NA                       |

#### Two or more regulator stages

5v

@ 47W

| C  | itical Messages                                                                                                      |

|----|----------------------------------------------------------------------------------------------------------------------|

| Me | ssages                                                                                                               |

| -  | ssages<br>[Power 33-427] The calculated current 55.409 A exceeds the board_85V supply<br>current budget of 55.000 A. |

#### Power Supply

| Supply Source | Voltage (V) | Total (A) | Dynamic (A) | Static (A) | Budget (A)  | Margin (A) |

|---------------|-------------|-----------|-------------|------------|-------------|------------|

| Vccint        | 0.850       | 47.652    | 36.324      | 11.328     | 50.000      | 2.348      |

| Vccint_io     | 0.850       | 7.113     | 6.227       | 0.886      | 4.000       | -3.113     |

| Vccbram       | 0.850       | 0.644     | 0.244       | 0.400      | 1.000       | 0.356      |

| Veccur        | 4 000       | 0.074     | 0.205       | 4 006      | Unoncoified | NIA        |

| Source              | Voltage (V)      | Total (A)     Bud     | lget (A) | Margin (A)                 |

|---------------------|------------------|-----------------------|----------|----------------------------|

| board_85V           | 0.850            | 55.409                | 55.000   |                            |

| Vccint<br>  Vccbram | 0.850<br>  0.850 | 47.652    <br>  0.644 | 1.000    | 2.348 (MET)<br>0.356 (MET) |

| Vccint_io           | 0.850            | 7.113                 | 4.000    | -3.113 (VIOLATED)          |

CCINT

CCBRAM

CCINT IO

## **Vivado Commands**

### **Vivado Power Optimization commands**

- Vivado has some powerful options that can save up to 30% on dynamic power

- Intelligent Clock Gating

- Power optimization available via the following commands:

- power\_opt\_design

- opt\_design

- power\_opt\_design can be run before or after placement

- Best results before placement

- After placement it will preserve timing

- > opt\_design

- Runs Block RAM power optimizations Can impact timing

- Disabled via -directive NoBramPowerOpt

### **Potential Power Impact of Place & Route directive**

| Synthesis            | opt_design            | Place                  | Route           |

|----------------------|-----------------------|------------------------|-----------------|

| AreaOptimized_high   | ExploreArea           | ExtraNetDelay_high     | HigherDelayCost |

| AlternateRoutability | ExploreSequentialArea | ExtraPostPlacementOpt  |                 |

|                      | ExploreWithRemap      | WLDrivenBlockPlacement |                 |

|                      |                       | SSI_SpreadLogic_high   |                 |

|                      |                       | SSI_HighUtilSLRs       |                 |

|                      |                       |                        |                 |

|                      |                       |                        |                 |

Examples of what we have found beneficial for power

- Every design is different experiment to understand the impact to Timing and Power

- The earlier in the flow the better the results i.e Synthesis and opt\_design

- •flatten\_hierarchy full generally improves power

### **Power Design Closure Conclusions**

Utilize Timing Closure to get the best understanding of Design Power Tcl Script for Timing and Power Closure - <u>AR 76056</u>

Largest Dependency on user input out of all Design Closure steps

User application Power Delivery, Ambient and Thermal solution information critical

Thermal Data should be used to refine Power Estimation Ensuring a successful Power Delivery and Board design

Power impacts every design

If not correctly addressed can have the largest Time To Market Impact

## **XILINX**®

## **Thank You**

### **Additional Resources**

- Xilinx Power Page Xilinx.com/power

- Vivado Power Analysis & Optimization User Guide UG 907

- UltraFast Design Methodology User Guide UG949

- Vivado Design Suite Tcl Command Reference Guide UG835

- Xilinx Power Estimator User Guide

- Versal ACAP UG1275

- UltraScale Plus <u>UG440</u>

- Power & Thermal Checklist <u>AR 76055</u>

- Tcl Script for Timing and Power Closure <u>AR 76056</u>