# Xilinx Accelerated Algorithmic Trading

Hardware Accelerated Algorithmic Trading Made Easy

Hamid Salehi March 2021

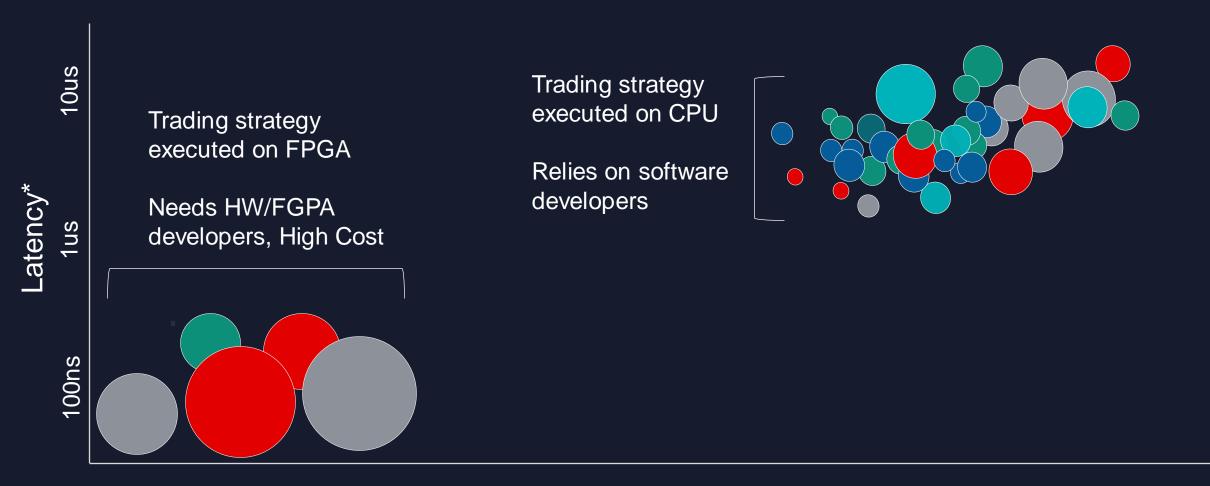

### **Algorithmic Trading Today**

**Algorithmic Complexity**

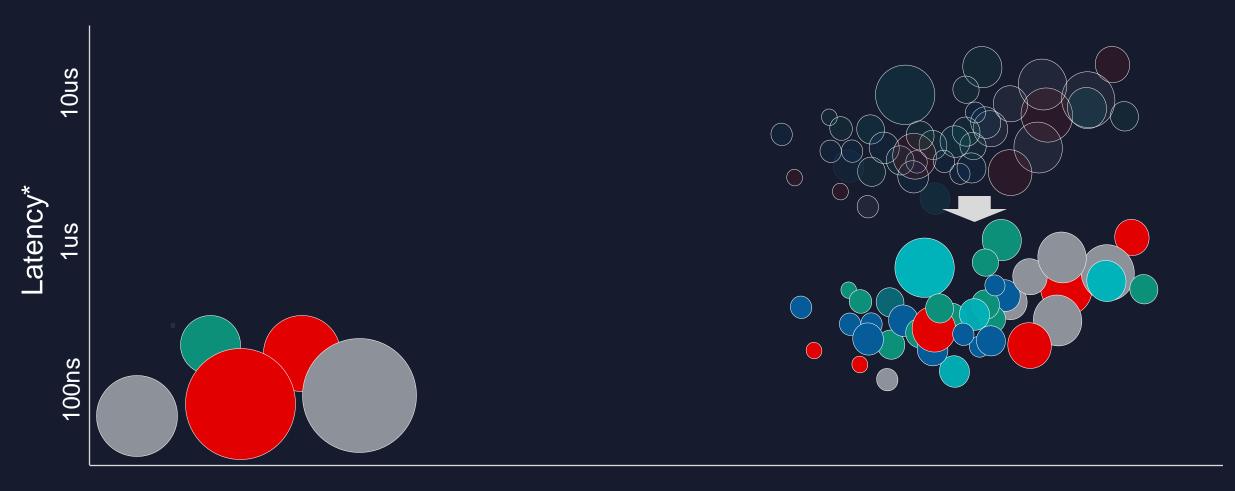

# The Challenge: Reduce Latency Without HW Design

**Algorithmic Complexity**

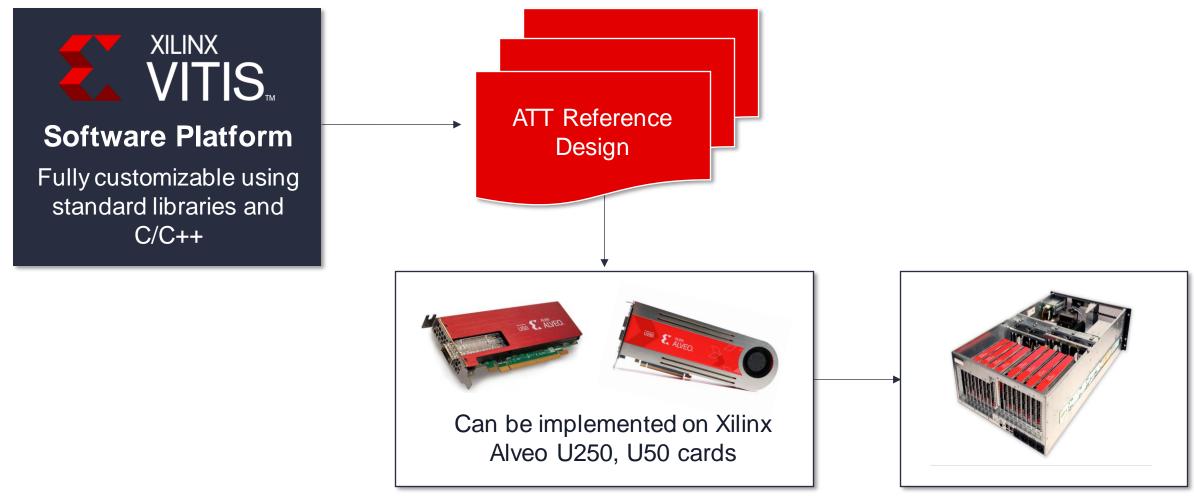

# Introducing Xilinx Accelerated Algorithmic Trading (AAT)

Customizable, open-source trading reference design with sub-microsecond latency

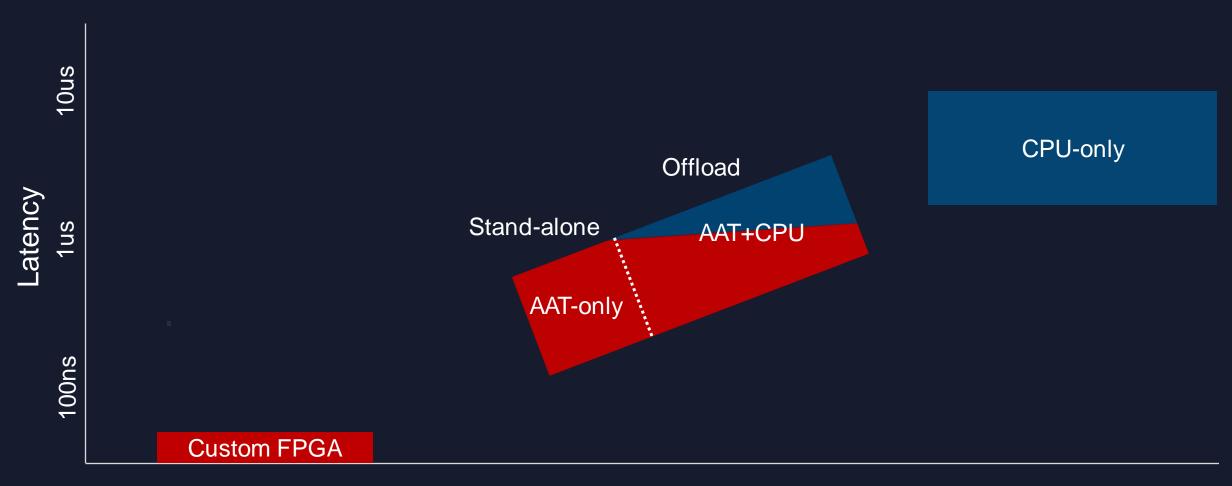

#### Use AAT as Standalone Accelerator or for CPU Offload

**Algorithmic Complexity**

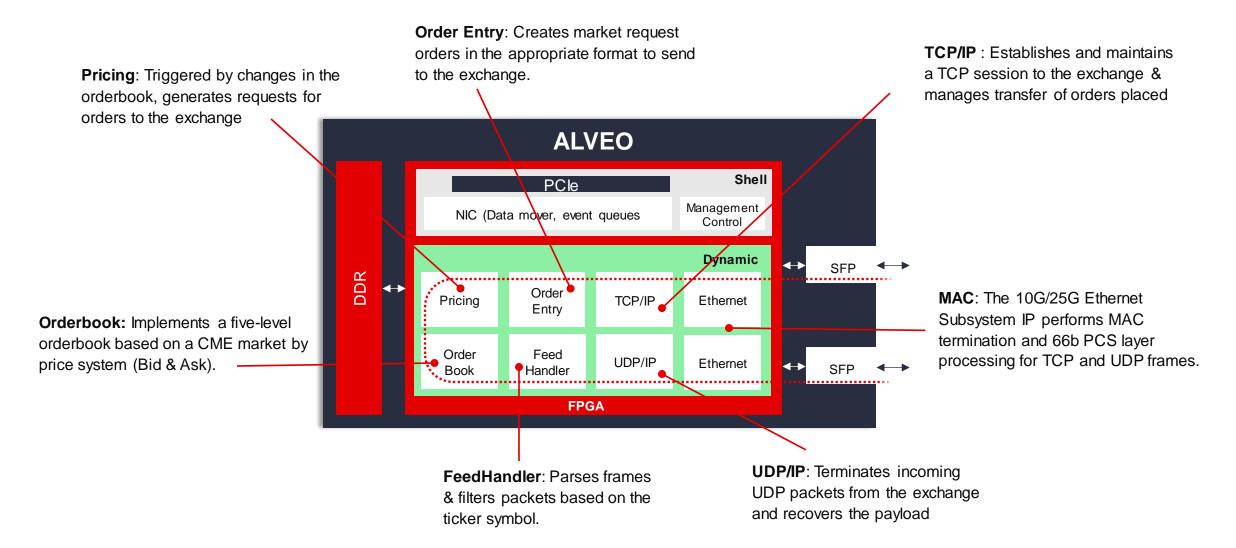

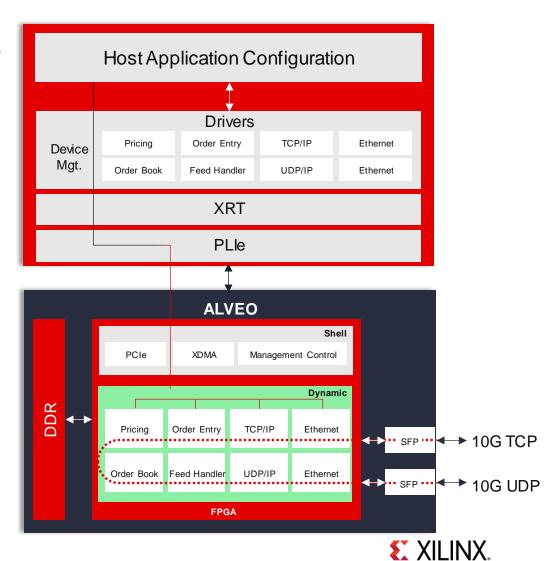

# **ATT Modular Design Explained**

Each module can be used as is, or customized to create a tailored trading solution

### Designed to accelerate migration from CPU to FPGA

The building blocks to enable software development of an electronic trading system on Xilinx Alveo products

- ✓ Fully written in HLS

- ✓ Designed for Software Engineers

- ✓ Integrated with Vitis

- ✓ Runs out the box on Xilinx Alveo

- Example HLS Code provided

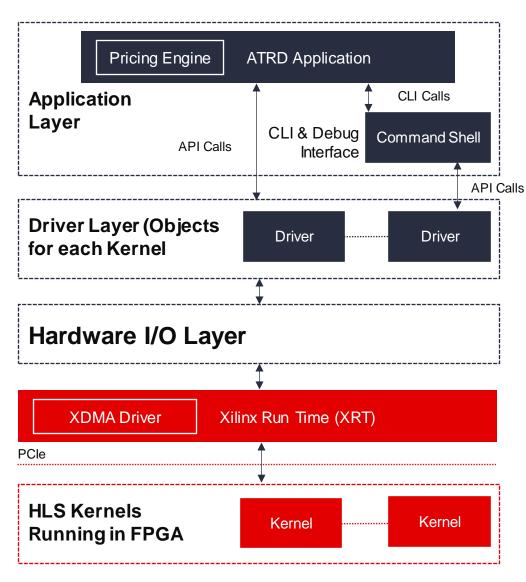

# Software Overview of AAT Reference Design

- Application Layer

- Command shell provides easy interface with help functionality

- Driver layer (User space)

- One driver for each kernel running on FPGA

- Hardware I/O Layer

- ▶ XRT (Xilinx Run Time)

- HLS kernels running on FPGA

## Who Can Benefit From AAT Reference Design

Pre-Trade Risk | Tick To Trade | Algorithmic Trading | Smart Order Routing | Market Data Accelerator | FIX Gateway

#### Get Started With Xilinx Accelerated Algorithmic Trading

Regain the latency edge

www.xilinx.com/applications/data-center/financial-technology/accelerated-algorithmic-trading.html

# Thank You