# Agenda

SmartNIC Evolution and Industry Challenges

▶ Introducing the SN1000 Composable SmartNIC

Architecture and Use Cases

### The Composable Datacenter

# There Is No "Typical" Datacenter

Requires not just disaggregated compute, network, and storage...

...but composability of the *device* itself

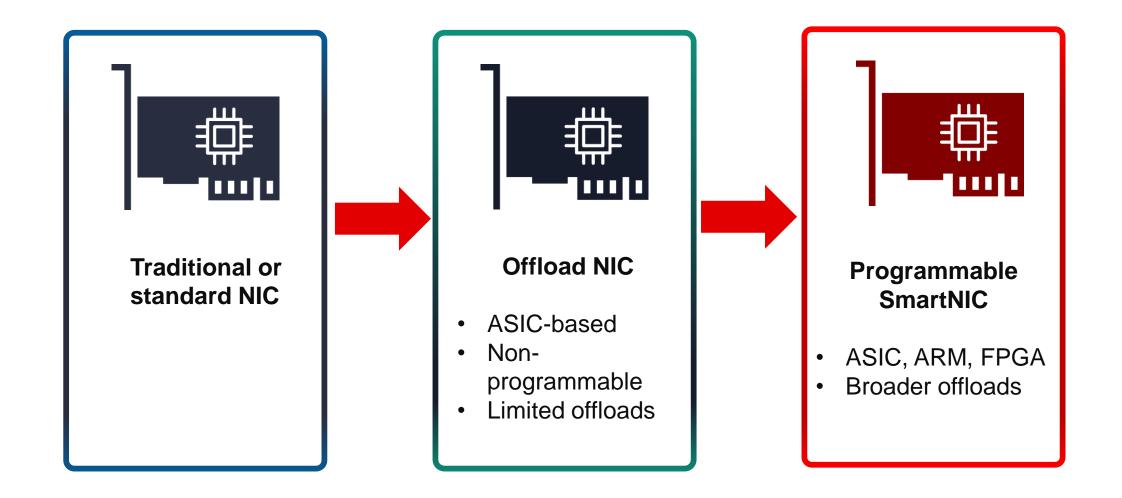

#### **Evolution of the NIC**

#### **SmartNICs: Emerging Limitations**

#### Cloud providers need both performance and adaptability

- Fast pace of change

- Wide variety of network functions

- Every Hyperscaler and CSP has different needs

# BUT...

ASIC implementations lack customization capabilities

CPU/SOC implementations suffer performance hits at scale

The Industry's First SmartNIC with *Composable Hardware*

## **SN1000 SmartNIC Summary**

#### Hardware

- 100G

- PCle Gen3 x16 or Gen 4 x8

- QSFP28 Direct Attach Copper | SR Optical

- 75W

- Form Factor: FHHL

#### **Net. Offloads/Virtualization**

- Stateless and Tunneling Offloads

- SR-IOV, Multiqueue

- VirtIO-net

- vDPA

#### **Networking Acceleration**

- Onload®

- DPDK Poll Mode Driver

- OVS

#### **Storage Acceleration**

- VirtIO-blk

- CEPH RBD Client Offload

#### **FPGA**

- 1M+ LUTs

- Memory: 2x 4GB x 72 (FPGA)

#### On board CPU

- Up to 16-core A72

- Memory: 1x 4GB x 72

#### **FPGA Custom Acceleration Plugins**

- Networking, Storage, Security, Compute

- P4/RTL/HLS

#### **OS Support**

Linux

#### **Manageability and Pre-boot**

- PXE, UEFI w/ HII

- MCTP SMbus, MCTP PCIe, and PLDM

- Secure Firmware Upgrade

# **SN1000 Architecture**

Rip Sohan

#### **Conventional SmartNIC Bottlenecks**

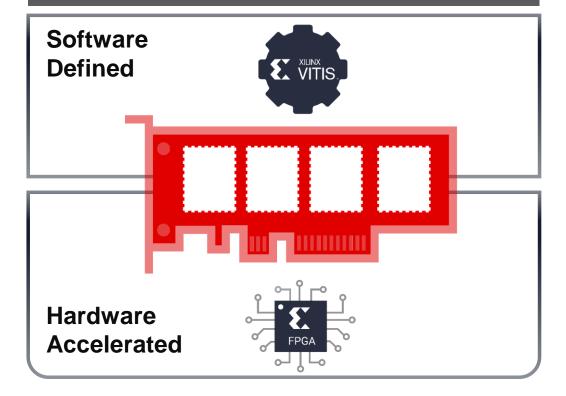

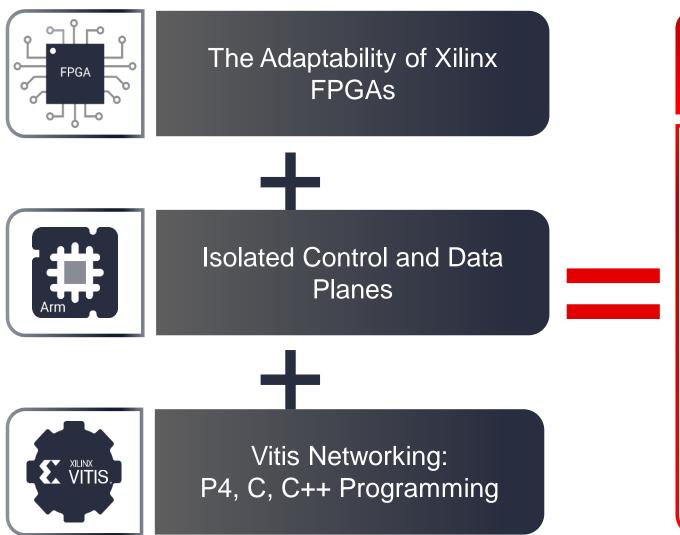

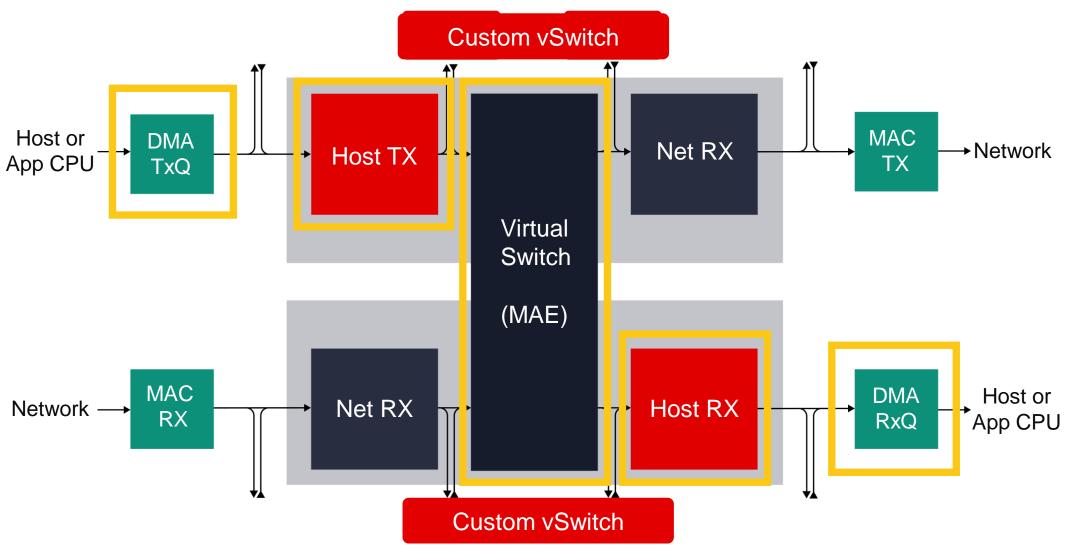

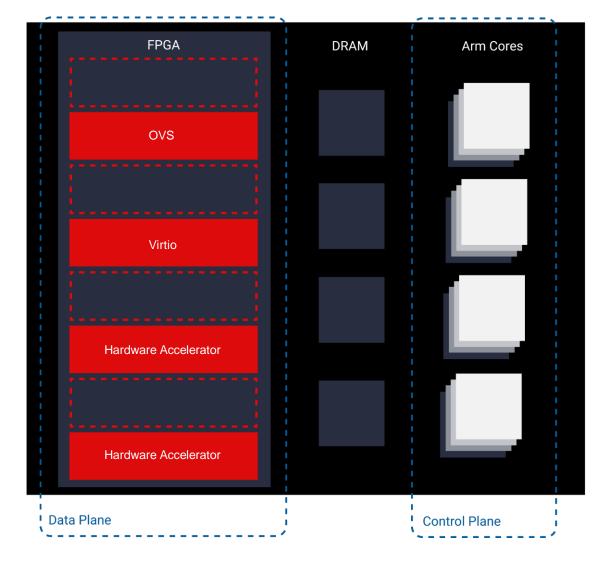

### The Xilinx Composable SmartNIC Architecture

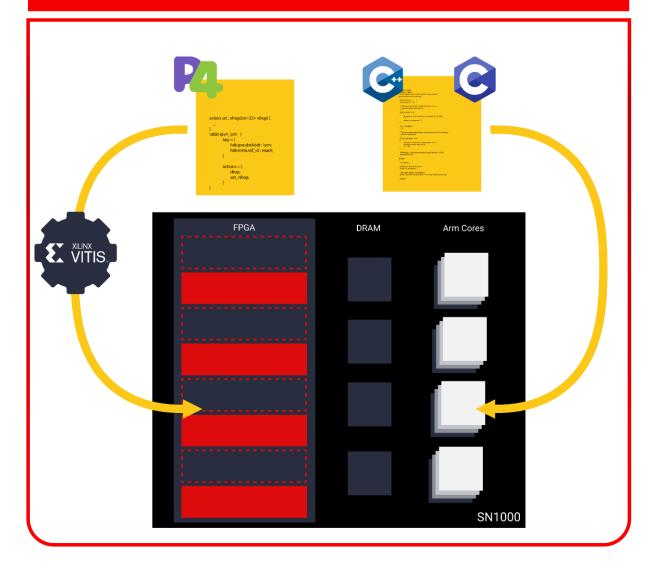

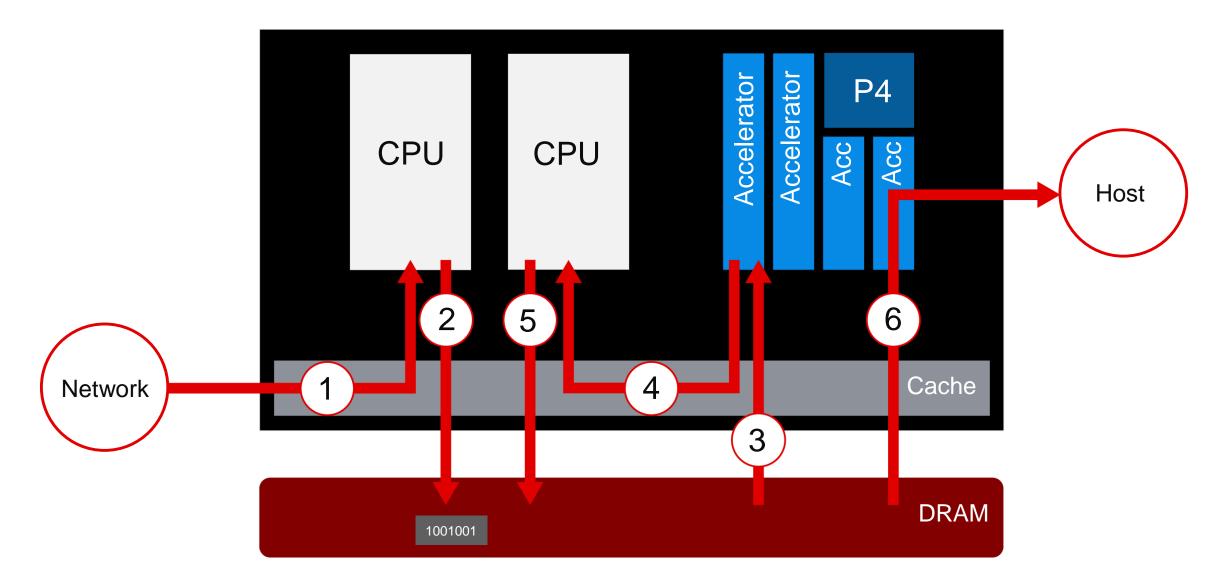

# **Support For Application-Specific Data Plane Accelerators**

Can be composed of Standard and Application Specific Accelerators

2 Can be chained to perform L2-L7 processing without requiring control or data transfer to on-board CPUs

3 Native support for P4 and HLS C/C++

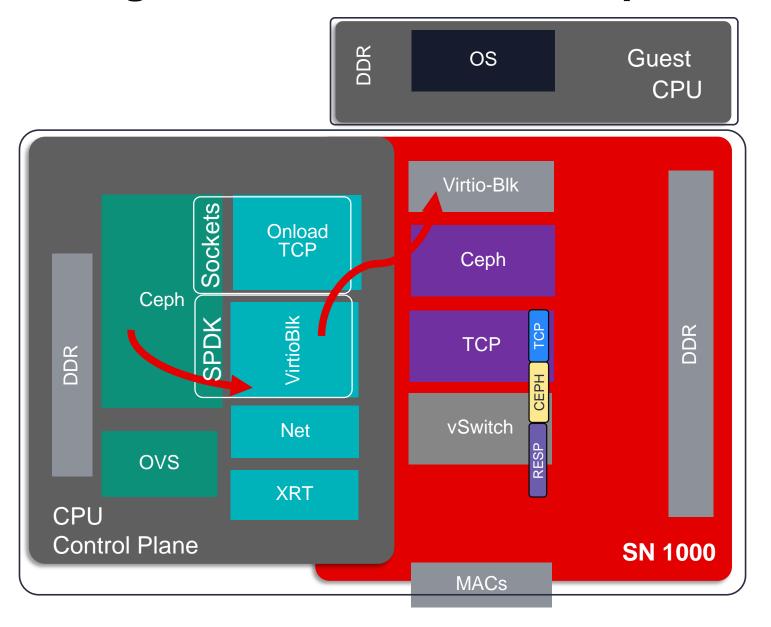

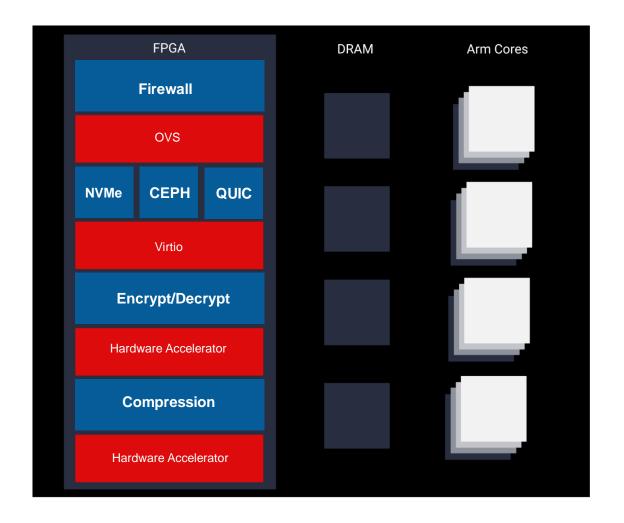

# **Example: Storage Virtualization on Composable NIC**

#### A Portable NIC Architecture

#### The SN1000 Difference

Software-defined hardware acceleration for all offloads

Application specific data paths at line-rate performance

P4, C, C++ programming for fast, adaptable hardware acceleration

Heterogeneous architecture with control and data plane isolation

# Thank You

## **Common Offload Types**

### **Common Offload Types**

**BULK CRYPTO** IPSEC | SSL/TLS | KTLS | STATEFUL FIRE-WALL | MULTIPLE CI-PHERS | HARWARE ROOT OF TRUST IDS/IPS

SION/DECOMPRES-SION | HASH ACCELERA-` TION | NVME ACCELERA-TION | NVMEOF | DEDUPLI-CATION | ERASURE CODING | FLASH CON-TROLLER | VIR-TIO.BLK

**NETWORKING**

**SECURITY**

**STORAGE**

- Software-defined hardware acceleration

- Application specific data paths

- Build custom offloads or extend existing offloads to handle new protocols and applications

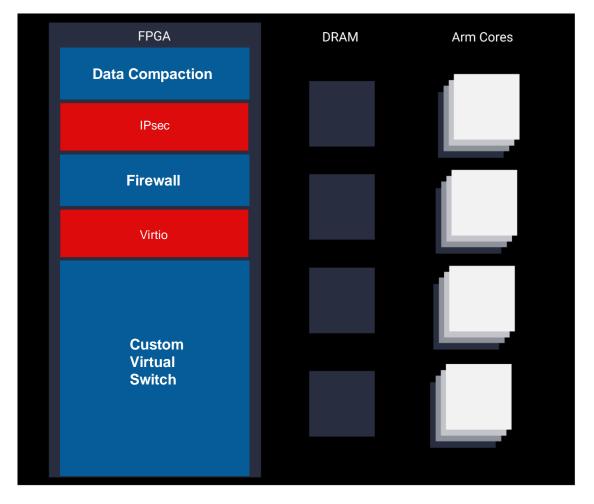

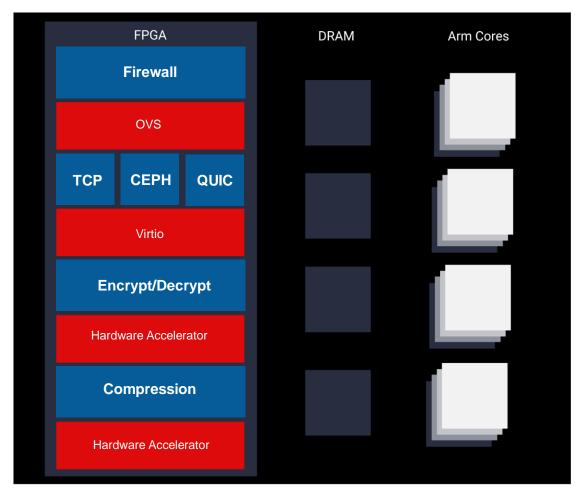

#### **Composability Example 2**

- Software-defined hardware acceleration

- Application specific data paths

- Build custom offloads or extend existing offloads to handle new protocols and applications

Example 1

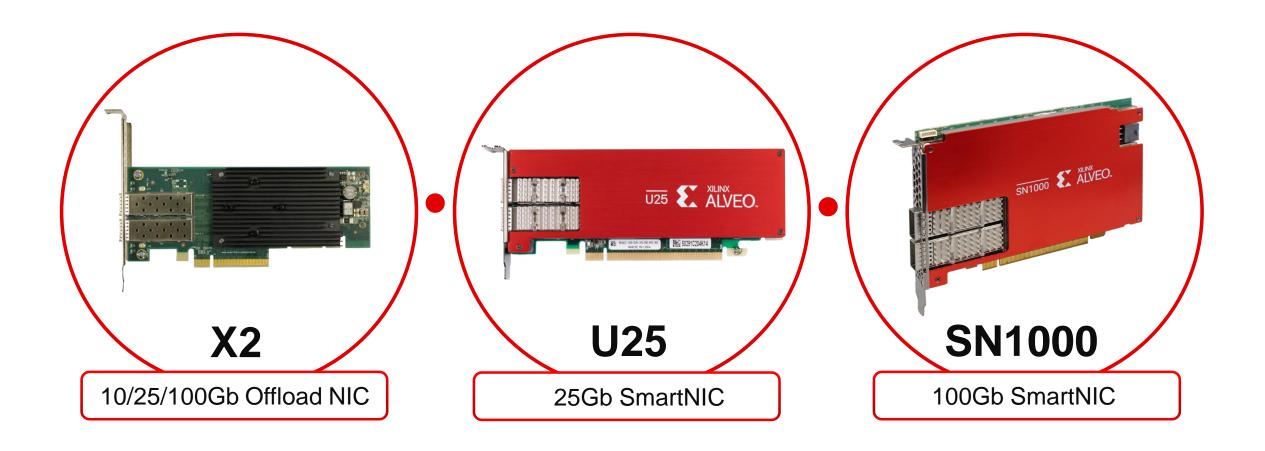

### **Xilinx NIC Family**

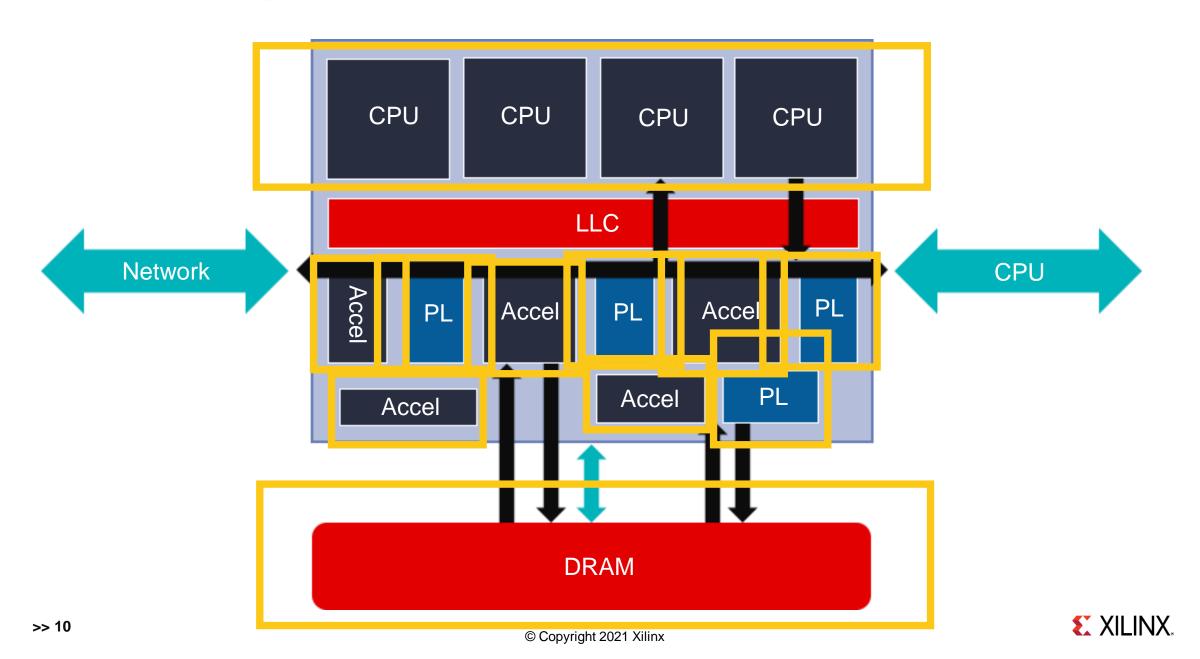

#### Composable Architecture

- Software-defined hardware acceleration

- Application specific data paths

- Build custom offloads or extend existing offloads to handle new protocols and applications

- Software-defined hardware acceleration

- Application specific data paths

- Build custom offloads or extend existing offloads to handle new protocols and applications

#### **Vitis Networking**

- Customize with ease, without sacrificing performance

- P4: the perfect match for "Match-Action" processing

- Tailored for high-performance networking

- Includes high performance algorithmic CAM technologies

- Vitis RTL/HLS- Mature developer tools for any compute or storage offloads at HW speeds with powerful high level language support

- Xilinx SmartNIC Plug-In Framework

- Customizations can be easily embedded into the powerful SN1000 SmartNIC flow

#### **Software-Defined Hardware Acceleration**