## **Accelerating Hardware Development**

Ramine Roane VP Software & Al

Xilinx Adapt – Vivado 2020

## Why Adaptive Computing?

**CPU & GPU: Memory Map**

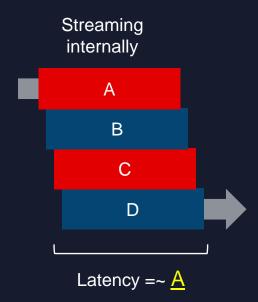

Latency = A+B+C+D + 6 \* memory latency

**FPGA: Streaming**

Streaming externally

## **Development Platforms**

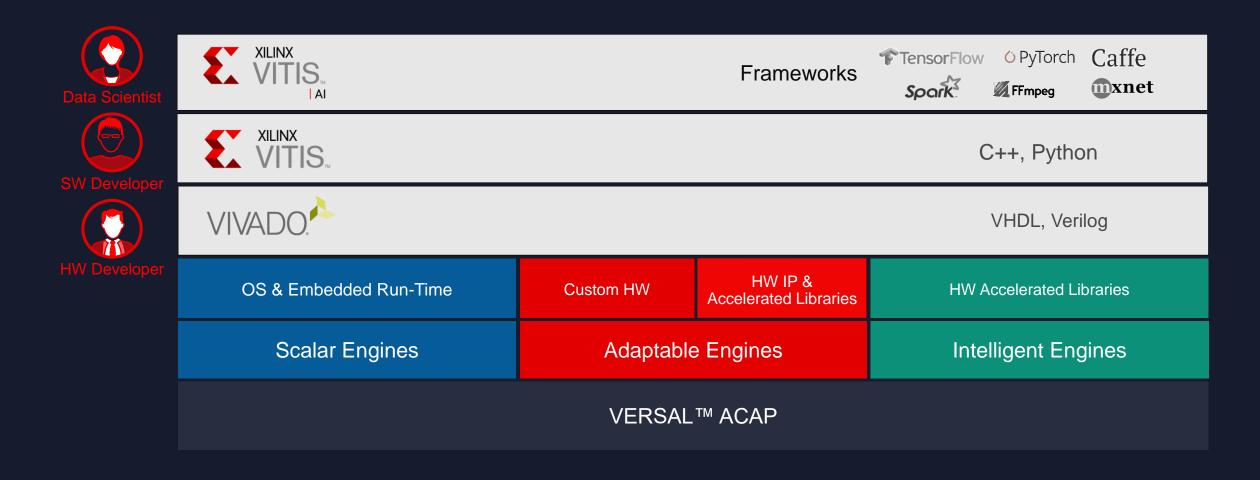

## **Top-Level Strategy**

**HW Developer**

Iterations: O(days)

3x-10x in 5y

**SW Developer** (HW aware)

Iterations: O(hour)

- C++ programming, libraries

- Memory hierarchy abstractions

- Pre-compiled libraries

**Data Scientist**

Iterations: O(minute)

Accelerated SW Frameworks (DSL, DSA)

## Adaptive Computing Challenges – \$250k in Prizes

- Developer Contest

- 1,070 participants registered on hackster.io

- > 70 countries

- Startup Contest

- 60 Startups registered on xilinx.com

2020 Contest is now closed, watch for the 2021 contest!

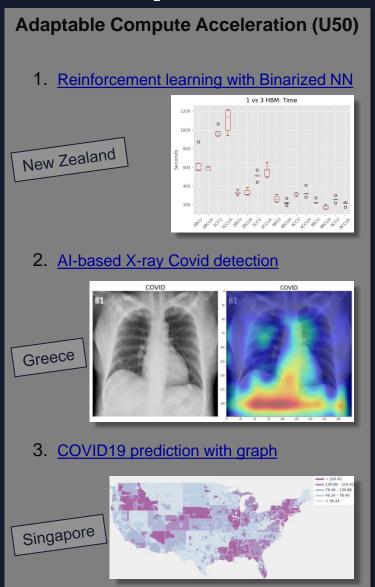

## **Developer Contest Winners: 9 Teams**

1. <u>Facemask Detector</u> (and thermal)

2. Automatic fall detection for elderly people

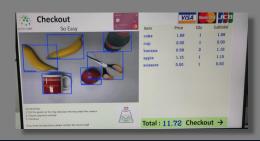

3. Real-time Smart PoS System

#### Adaptive IoT (U96)

1. Hand-gesture controlled drone

2. Real-time 3D Perception

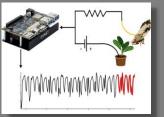

3. <u>Time Series Similarity Prediction</u>

## **Vivado – A modern EDA tool**

State-of-the-Art Technology

Methodology & Best Practices

System-level design & verification with Versal

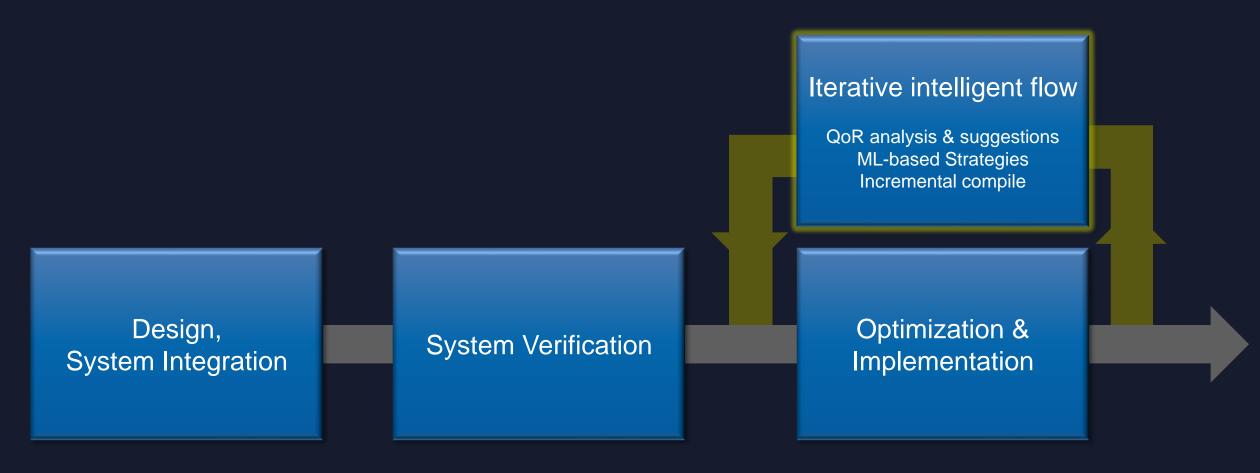

## Vivado Design Flow Overview

## **Compile Time Reduction**

#### Methodology

Guidelines for fastest design closure

- Best practices for design closure

- Board, RTL, constraints, P&R

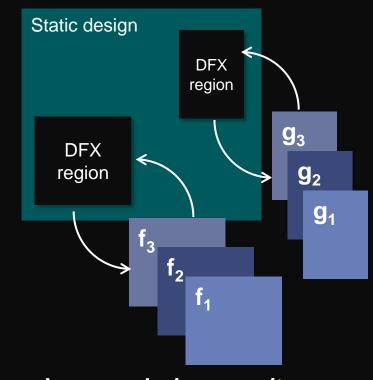

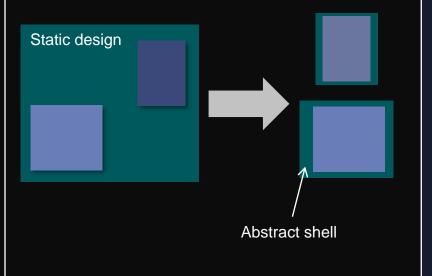

#### **Dynamic Function eXchange**

Time multiplexing of HW functions

- Increase device capacity

- Over the air update

#### **Abstract Shell for DFX**

Abstraction of the static design

- Compiles 2-10x faster

- Static design security

## **Design Cycle Reduction**

#### **IP Integration (RTL, HLS, MATLAB)**

IP-centric system integration

- Team design, CI, DFX

- Timing Closure at system level

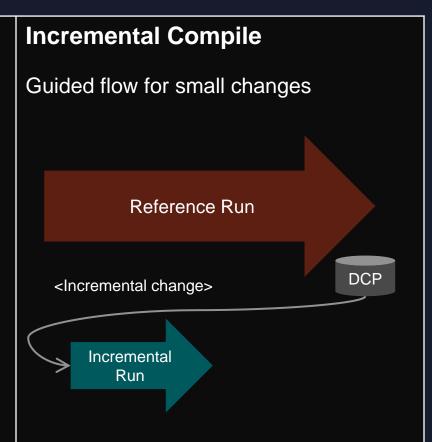

#### I<sup>2</sup> (intelligent iterative) Flow

QoR Analysis + ML strategies

- 10% automated QoR boost

- Expert in the box!

- 2x faster compile time

- Incremental synthesis and P&R

### **Recent Customer Successes**

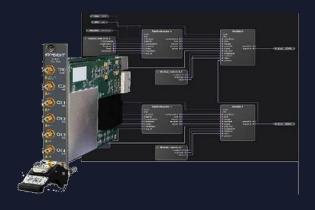

#### **PathWave FPGA**

**SBC3511**

**PXI** systems

66% compile time reduction w/ DFX & Abstract Shell

COTS vendor

DFX & Abstract Shell

I<sup>2</sup> flow helped meet timing in first attempt

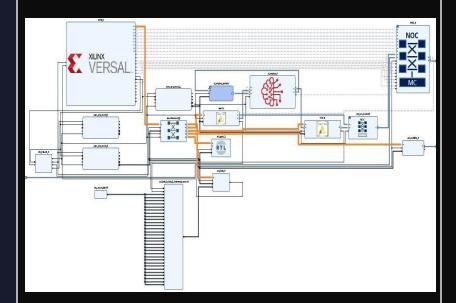

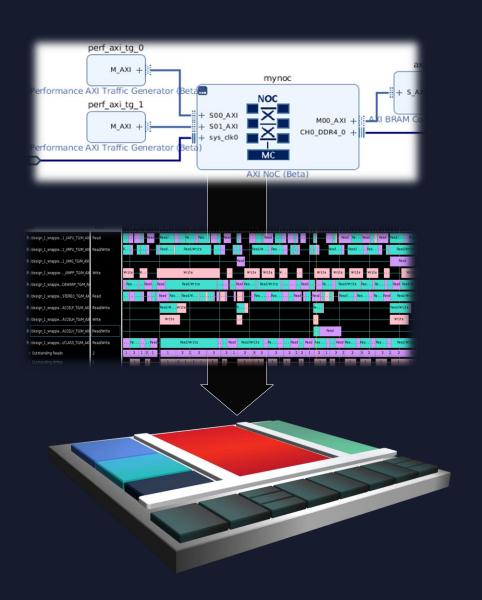

## **System Design for Versal**

IP Integrator design with NoC compiler

System-level traffic analysis

System co-simulation of PS, PL, AI Engine

Implementation & Hardware Debug

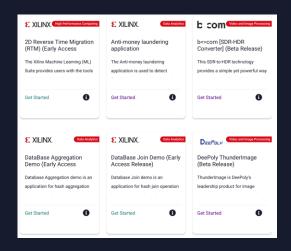

# Xilinx App Store Accelerate Everything.

View App Catalog

Xilinx.com/AppStore

## Three-Step, Ten-mins to Evaluation on Alveo or Cloud

### Step 1: Select an app

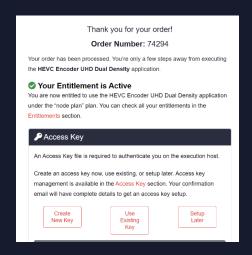

## Step 2: Entitlement

## Step 3: Download & Run

docker pull hubxilinx/vnova\_pplus\_alveo\_u200:ppxde-demo

docker run -v /tmp/cred.json:/vnova\_pplus/cred.json:Z

### **Call to Actions**

Adopt Vivado methodologies & latest features <sup>12</sup> Flow, Abstract Shell, DFX

▶ Try out new tutorials on GitHub

Contribute to the Xilinx App Store

Monetize you IP or Application

## Thank You