# An Introduction to Vitis HLS

## High-Level Synthesis (HLS) Flows

## Technical Overview + Demo Examples

>> 2

> Higher Productivity !

- Concise code

- Fast C simulation

- Automated Simulation of Generated RTL

- Optimized Libraries

# ... int main () { // test vectors ... int foo() { // foo to become hw ... } ... }

# **Applications for High-Level Synthesis**

Surveillance, Al Classification

Recognition

Radar, Sonar

> Drones

> Micro-controller, Al

#### **Communications**

- > LTE MIMO receiver

- > Advanced wireless antenna positioning

Industrial, Scientific, Medical

Ultrasound systems

Aerospace and Defense

**Signals Intelligence**

Motor controllers

#### Audio, Video, Broadcast

- **>** 3D cameras

- > Video transport

#### Automotive

- Infotainment

- Driver assistance / Al

**Test & Measurement**

Semiconductor ATE

**Communications instruments**

#### Consumer

- > 3D television

- > eReaders

- > High performance computing

- > Database acceleration

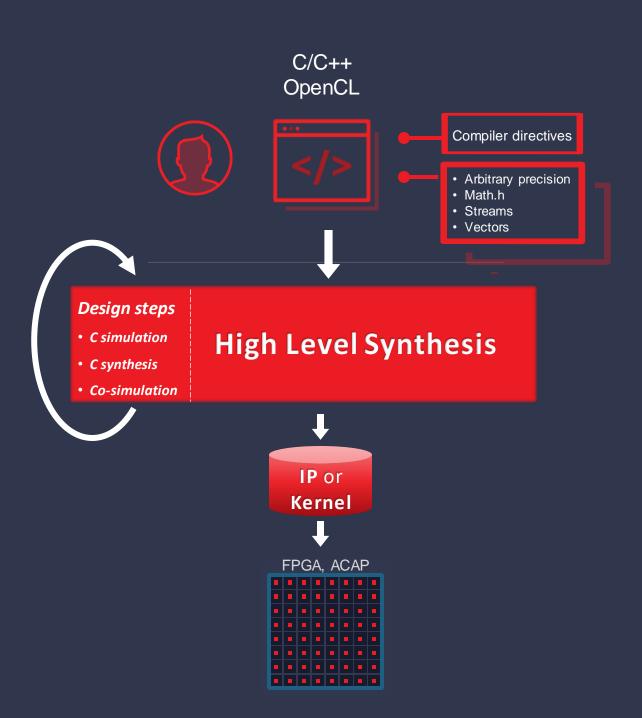

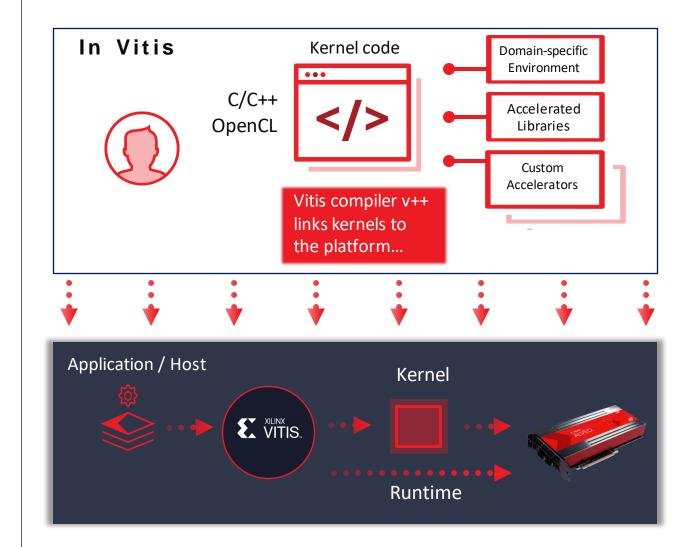

# **HLS in Vitis Flow**

#### **HLS compiles C-based Kernels**

- $\checkmark$  V++ performs all the compiles and links

- ✓ HLS is automatically invoked

- $\checkmark~$  No necessary direct interaction with HLS

- ✓ HLS reports imported in Vitis Analyzer

- ✓ Full application can be C-based

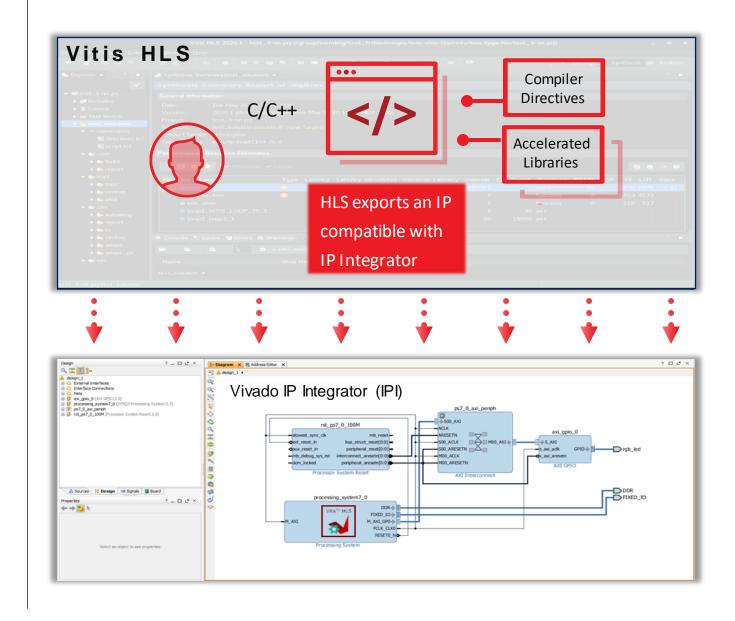

# **HLS in Vivado Flow**

#### HLS exports RTL IP...

- ✓ User runs HLS directly

- ✓ Typically block assembly done in IPI

- ✓ Design entry is C/C++

- ✓ Can invoke Vivado waveform viewer

## High-Level Synthesis (HLS) Flows

## Technical Overview + Demo Examples

>> 9

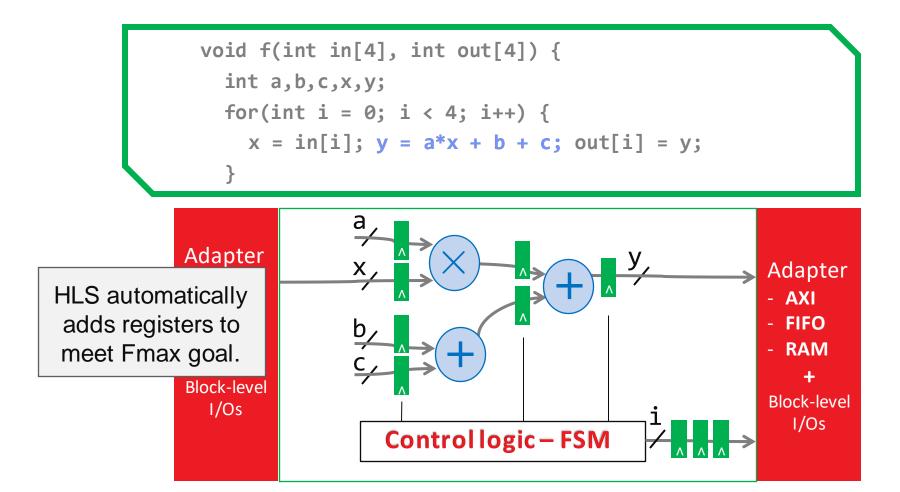

# **Automatic Interface and Control Logic**

> Simple C code quickly become a kernel or an IP...

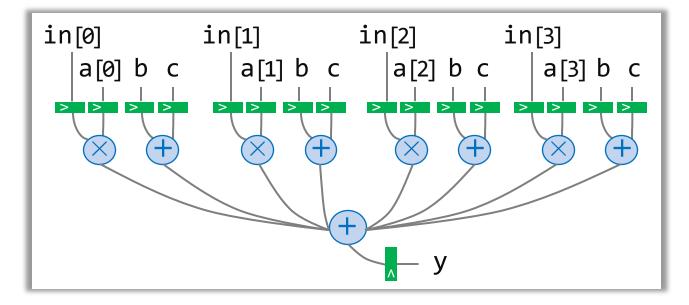

# **Design Space Exploration via Pragmas**

> Pragmas change the circuit topology...

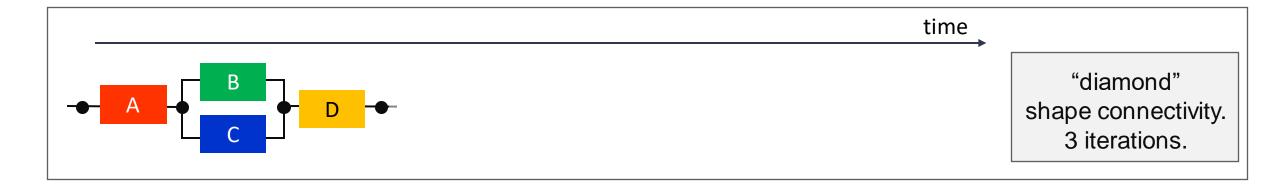

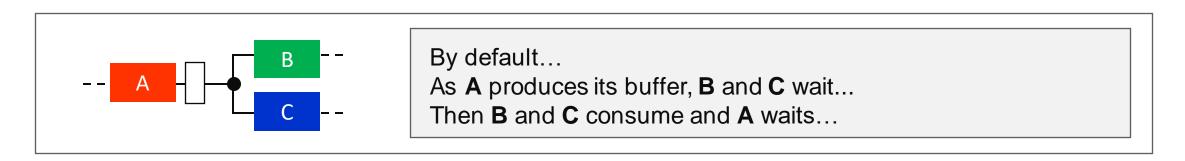

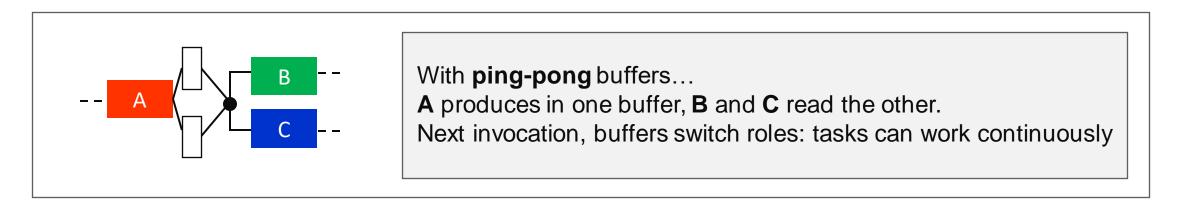

## **Task Parallelism with HLS**

© Copyright 2020 Xilinx

Default versus ping-pong buffers

#### The dataflow pragma in HLS automates memory expansion to enable task parallelism

**E** XILINX.

# **Vectorized Data Types...**

```

// Vectorization means that the compiler detects that

// independent instructions can be executed as SIMD instructions.

// So, something like this...

for(i=0; i<N; i++){</pre>

a[i] = a[i] + b[i];

// ... becomes "vectorized" as... (using vector notation)

for (i=0; i<(N-N%VF); i+=VF){</pre>

a[i:i+VF] = a[i:i+VF] + b[i:i+VF];

// 1 operation that can be done on VF elements of the array

// at the same time and does this N/VF times instead of doing

// the single operation N times...

```

# **Vectorized Data Types in Vitis HLS**

- > Vitis HLS supports the C++14 vector\_size attribute

- Simply using C++...

// vector\_size specifies size in bytes

typedef float float16 \_\_attribute\_\_(vector\_size(64));

Custom vector type float16 based on C++ attribute

- > ... and also supports arbitrary precision types via hls\_vector.h

- >> Examples

#include "hls\_vector.h"

using float16 = hls::vector<float, 16>;

Same as above using hls::vector

#include "hls\_vector.h"

using quad = hls::vector<ap\_int<18>, 4>;

Vector of four 18-bit signed variables

# **Vectorized Data Types – Operations**

#### > Initialization

| <pre>hls::vector<int,< pre=""></int,<></pre> | 4> x; /                     | / uninitialized                           |

|----------------------------------------------|-----------------------------|-------------------------------------------|

| <pre>hls::vector<int,< pre=""></int,<></pre> | 4> y = 10; /                | / scalar initialized                      |

| <pre>hls::vector<int,< pre=""></int,<></pre> | $4 > z = \{0, 1, 2, 3\}; /$ | / initializer list (must have 4 elements) |

#### > Access

myvec[i] = ...; // reference to an element

... = myvec[i]; // value of an element

#### > Recommendations

- >> Use hls::vector<T, N> with N as a power of 2 for a better alignment that guarantees smaller initiation interval (II)

- >> Use the \_\_attribute\_\_((no\_ctor)) for better II when using dataflow

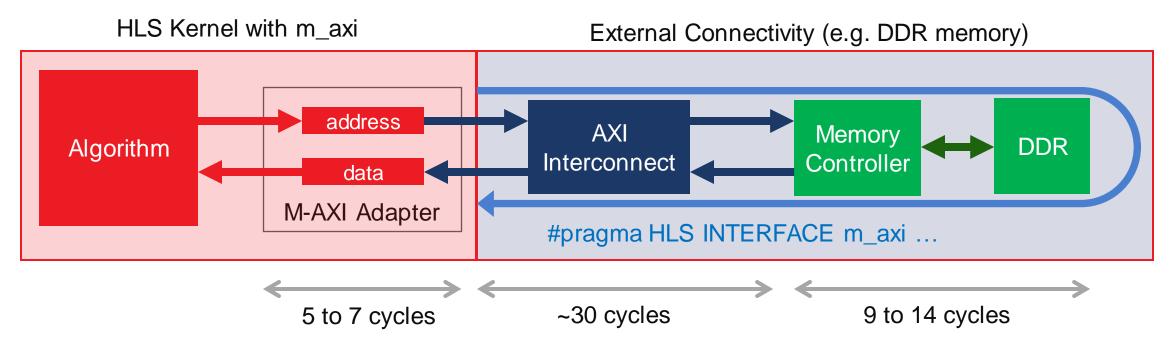

# **Optimizing Interfaces**

#### > Efficient Pipeline

>> Adapt the latency parameter of the interface for efficiency

#### > Loop Bursts

- >> Segmented into smaller bursts by the adapter (and that's okay!)

- >> Adapter will pipeline for you (independent state machine!)

# Demo #2 – Vector types and AXI Interfaces

## High-Level Synthesis (HLS) Flows

## Technical Overview + Demo Examples

>> 20

## **Resources – HLS**

#### > HTML and PDF User Guides

#### > Basic examples

>> Github examples accessible from Vitis HLS

#### > Tutorials and complete examples

- >> Github libraries: Vitis\_Libraries

- >> Vitis examples: <u>Vitis\_Accel\_Examples</u>

#### > Forums

>> Monitored by Xilinx support staff

#### Vitis HLS used both in Vitis and Vivado

## C based entry boosts productivity

Get started with examples and tutorials