# Next-Generation Zynq UltraScale+ RFSoC

David Brubaker Product Line Manager, Zynq® UltraScale+™ RFSoC

### Industry's only single-chip adaptable radio platform

High channel count with up to 50% power and footprint reduction

### Now delivering up to 6GHz of direct-RF sampling

Flexible, multiband radio for 5G wireless, radar, cable access, and a breadth of RF-applications

### Xilinx is an RF-analog leader meeting current & future market needs

Keeping pace with market deployment needs and committed to integrated RF sampling

# **Analog World**

# **Digital Processing**

1010101010<sup>1</sup>

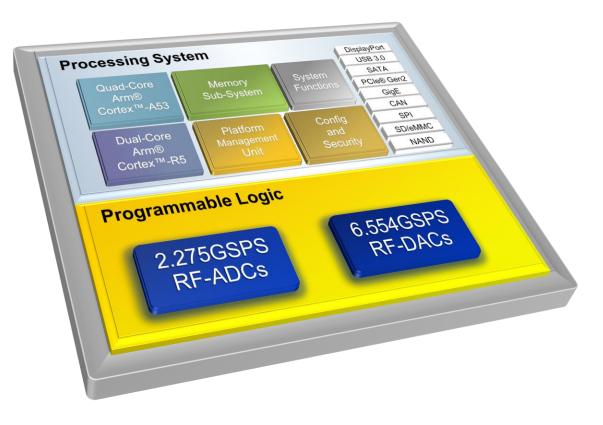

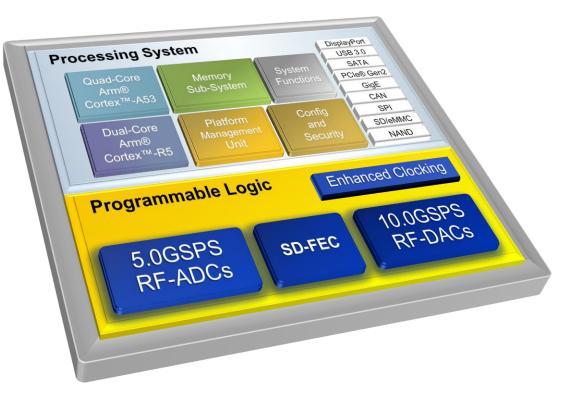

### Zynq UltraScale+ RFSoC The First Hardware Programmable RF System-on-Chip (RFSoC)

Integrated RF-Class Analog

Soft-Decision Forward Error Correction (SD-FEC)

Software

Flardware

FPGA

SD-FEG

33

Anala

11

Real Time

ARNA

curity & Sareny

II WALL A STANDER

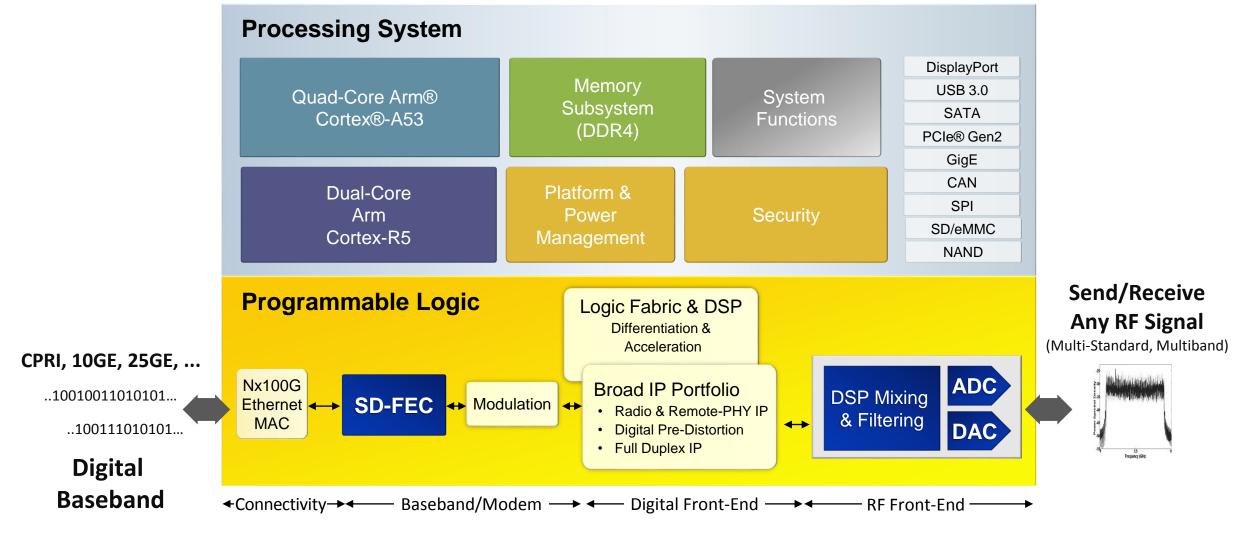

# **Single-Chip Adaptable Radio Platform**

### **Integrating the RF Signal Chain**

# Key Target Markets and a Breadth of RF-Applications

WirelessRemote<br/>Radio5G<br/>BasebandmmWaveImage: Signal systemImage: Sign

- > Power & Footprint for mMIMO

- > LDPC for 5G Baseband

- > IF Digital Transceiver for mmWave 5G NR

- > Single-Chip Solution for DOCSIS 3.0 and 3.1

- > Supports Extended Spectrum DOCSIS

- > Adaptable HW for Future-Proofing

- > SW & HW Reconfigurable> Full L-Band & S-Band Sampling

- > Partial C-Band Direct Sampling

- > LiDAR Systems in Automotive

- > Test & Measurement

- > Satellite Communications

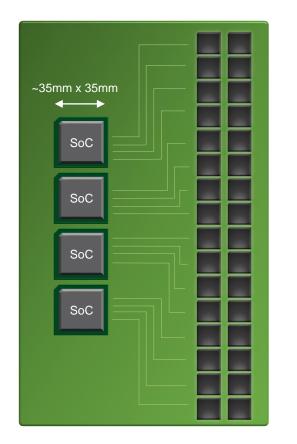

### Massive MIMO Radios Developed by Tier-1 Wireless Network Provider

50% Less Power75% Smaller Footprint

64x64

#### **Customer Problem**

Implementing 64x64 mMIMO requires up to 9X more IC components

### **Xilinx Solution & Differentiation**

- > Four Zynq® UltraScale+™ RFSoCs

- > IC count reduced from 36 to 4

- > Significantly less power and footprint

### Xilinx System Content Increased by Over 35%

### Modularity for Large-Scale Multi-Function Phased-Array- Radar (MPAR) Systems

Single-Chip 16x16 TRX Module Four ZU+ RFSoC TRX Modules per 64x64 TRX Panel Common Module for Diverse MPAR Systems

# Next-Generation Zynq UltraScale+ RFSoCs Greater Performance, Flexibility, and Integration

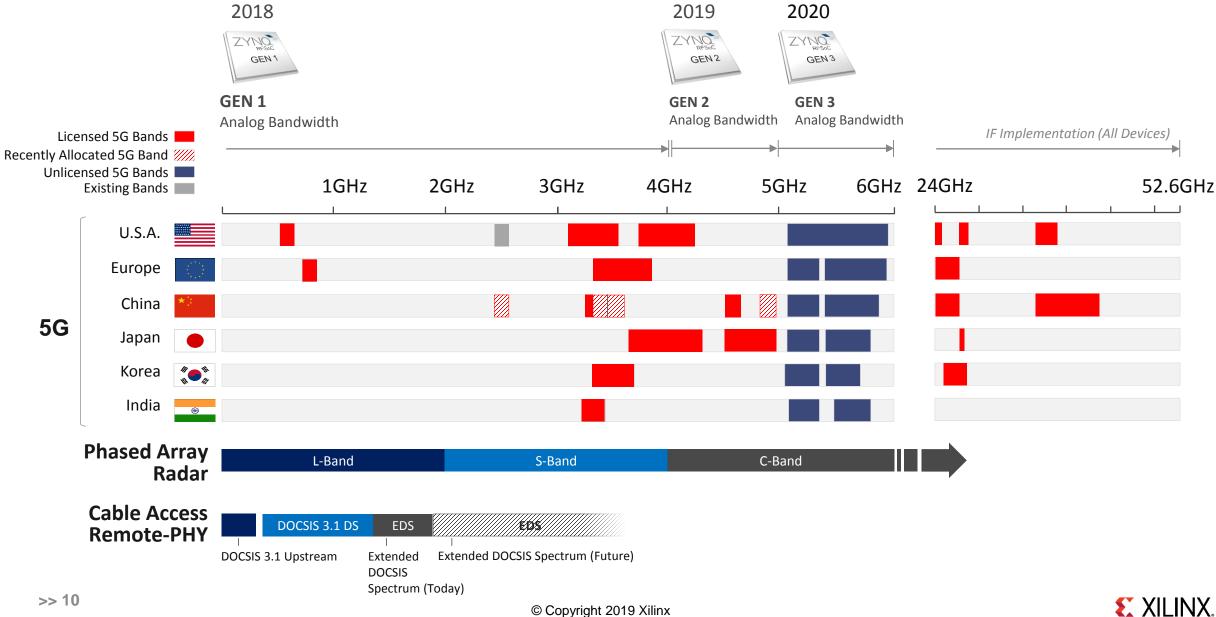

# **Portfolio Aligned with Market Requirements**

# Introducing Zynq UltraScale+ RFSoC Gen 2

### Meets timelines for 5G NR bands in Asia

- > Engineering Samples: NOW

- > Production: June 2019

- > Demo at MWC 2019

### Enhancements

- > Greater RF performance for 16x16 configuration

- > Scalable from base portfolio 16x16 device

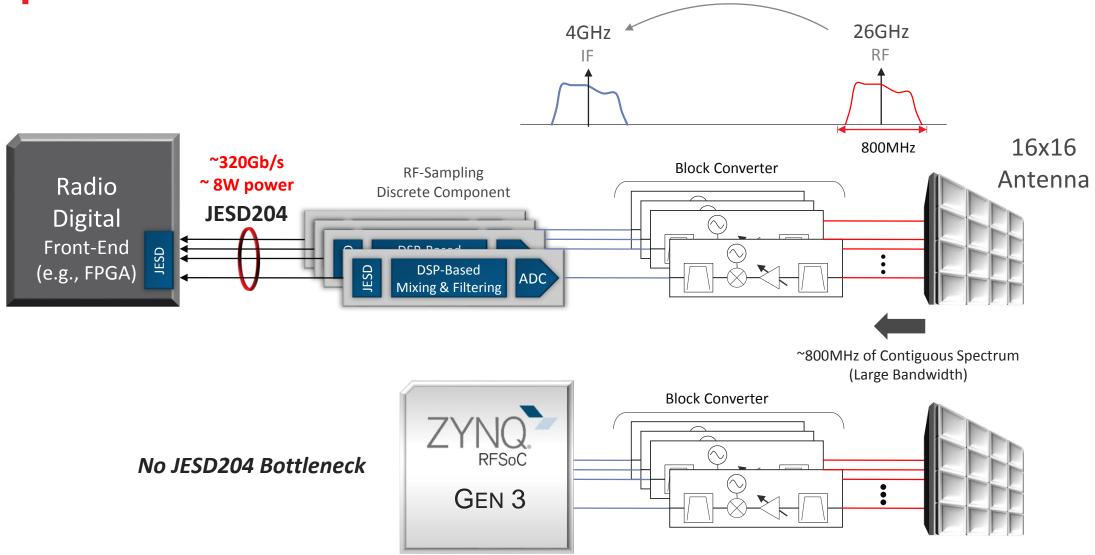

# Introducing Zynq UltraScale+ RFSoC Gen 3

#### Extended RF performance for more use cases

- > Full Sub-6GHz Direct-RF support

- > 14 bit performance

- > Up to 20% power reduction in RF-DC for TDD use case

- > Extended mmWave interfacing

#### Reduced BOM and system cost

- > Enhanced clocking distribution simplifies PCB board design

- > Eliminates onboard clocking component cost

#### Simplified design and greater flexibility

- > Full multiband, multi-standard support

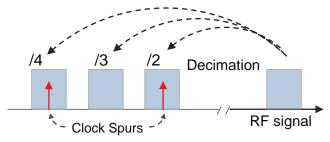

- > Additional interpolation and decimation simplifies frequency planning

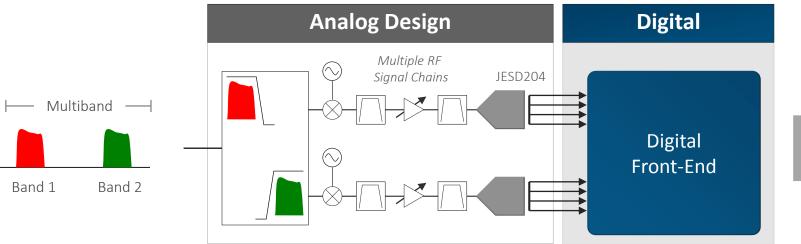

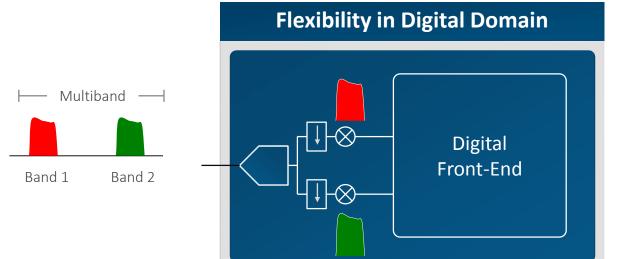

# Multiband, Multi-Standard Reconfigurable Platform

#### Complex RF Signal Chains

Multiple Platforms for Different Radio Configurations

Single Platform Multiband Reconfigurable

### Extended Intermediate Frequency (IF) Implementation for mmWave

# Zynq UltraScale+ RFSoC Gen 2 & Gen 3 Product Table

|                                           |                                    | Gen 2                                                                      | Gen 3                |                           |                      |                           |  |  |  |  |  |

|-------------------------------------------|------------------------------------|----------------------------------------------------------------------------|----------------------|---------------------------|----------------------|---------------------------|--|--|--|--|--|

|                                           |                                    | n79 5G NR<br>Bands                                                         | FDD/<br>DPD Feedback | Radar &<br>Fixed Wireless | DOCSIS &<br>Backhaul | Radar &<br>Fixed Wireless |  |  |  |  |  |

|                                           |                                    | Radio Access Radi                                                          |                      |                           |                      |                           |  |  |  |  |  |

|                                           |                                    | ZU39DR                                                                     | ZU46DR               | ZU47DR                    | ZU48DR               | ZU49DR                    |  |  |  |  |  |

|                                           | 14-bit, 5.0GSPS ADC                | -                                                                          | 4                    | 8                         | 8                    | -                         |  |  |  |  |  |

| tal<br>in                                 | 14-bit, 2.5GSPS ADC                | -                                                                          | 8 –                  |                           | -                    | 16                        |  |  |  |  |  |

| Analog-Digital<br>Signal Chain            | 12-bit, 2.275GSPS ADC              | 16                                                                         |                      |                           |                      |                           |  |  |  |  |  |

| Analog-<br>Signal                         | 14-bit, 6.554GSPS DAC              | 16                                                                         |                      |                           |                      |                           |  |  |  |  |  |

| An<br>Si                                  | 14-bit, 10GSPS DAC                 | -                                                                          | 12                   | 8                         | 8                    | 16                        |  |  |  |  |  |

|                                           | SD-FEC                             | -                                                                          | 8                    | -                         | 8                    | -                         |  |  |  |  |  |

| <u>ب</u> ھ                                | Application Processor Core         | Quad-core Arm Cortex-A53 MPCore <sup>®</sup> up to 1.33GHz                 |                      |                           |                      |                           |  |  |  |  |  |

| tem<br>Log                                | Real-Time Processor Core           | Dual-core Arm Cortex-R5 MPCore up to 533MHz                                |                      |                           |                      |                           |  |  |  |  |  |

| syst<br>able                              | High Speed Connectivity            | DDR4-2666, PCIe Gen3 x16, 100G Ethernet (PCIe Gen4 x8 for Gen 3 ZU+ RFSoC) |                      |                           |                      |                           |  |  |  |  |  |

| Processing System &<br>Programmable Logic | Logic Density (System Logic Cells) | 930K                                                                       | 930K                 | 930K                      | 930K                 | 930K                      |  |  |  |  |  |

|                                           | DSP Slices                         | 4,272                                                                      | 4,272                | 4,272                     | 4,272                | 4,272                     |  |  |  |  |  |

|                                           | 33G Transceivers                   | 16                                                                         | 16                   | 16                        | 16                   | 16                        |  |  |  |  |  |

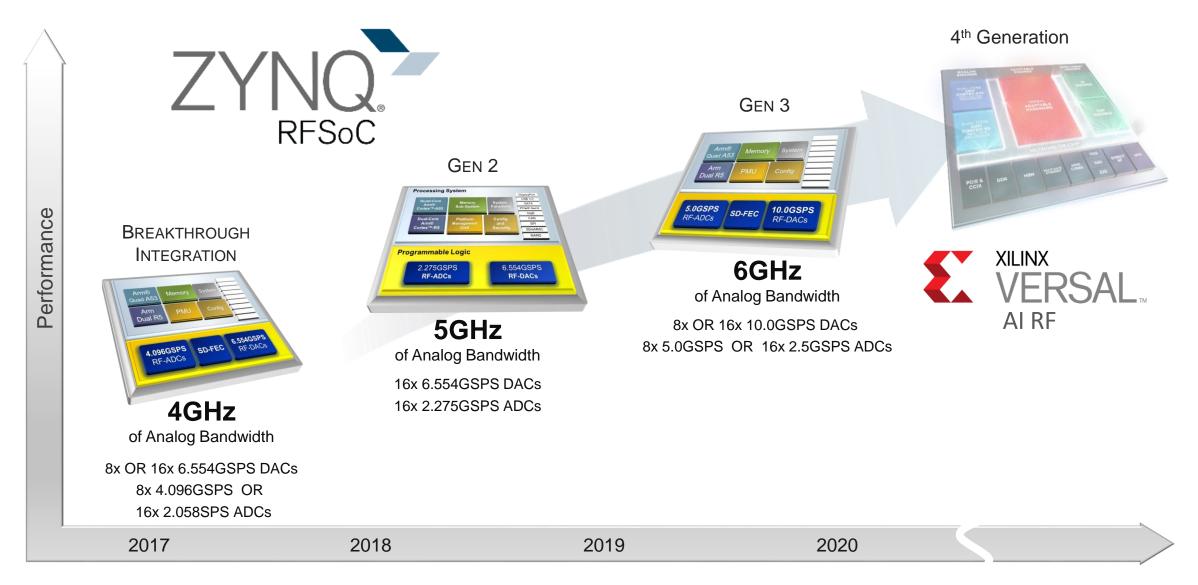

# Roadmap

© Copyright 2019 Xilinx

### **Roadmap to Meet Current and Future Market Needs**

**E** XILINX.

# Summary

### Zynq UltraScale+ RFSoC base devices in full production with multi-market success

- >4GHz of analog bandwidth

- > Industry recognized with multi-market success in wireless, cable access, and radar

- > A growing ecosystem of boards, tools, and IP

### Zynq UltraScale+ RFSoCs Gen 2

- > 5GHz of analog bandwidth

- > Timely support of the latest 5G bands for regional deployment

- > Sampling NOW. Production release in June 2019

#### Generation Zynq UltraScale+ RFSoCs Gen 3

- >6GHz of analog bandwidth for full direct-RF support of sub-6GHz bands, extended millimeter wave interface

- > Full multi-band support

- > Simplified clocking, more decimation, and interpolation options

#### Scalability and migration across the portfolio

# Adaptable. Intelligent.

© Copyright 2019 Xilinx

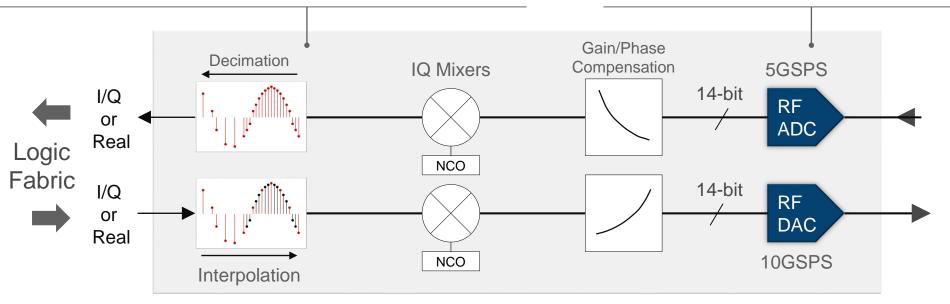

### **Enhanced DSP & Data Converters**

#### **Enhanced DSP Mixing and Filtering**

- > Additional interpolation/decimation for RF flexibility/freq. planning

- > (1x, 2x, 3x, 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, 24x, 40x)

- > Offloads DSP processing (filtering) from programmable logic

### **6GHz Direct RF Bandwidth**

- > 14-bit 5GSPS ADCs, 14-bit 2.5GSPS ADCs

- > SW programmable RF signal chain up to 6GHz

- > Optimal mix of ADCs for 8x8 FDD Implementations (Wireless)

#### **Enhanced DSP Mixing and Filtering**

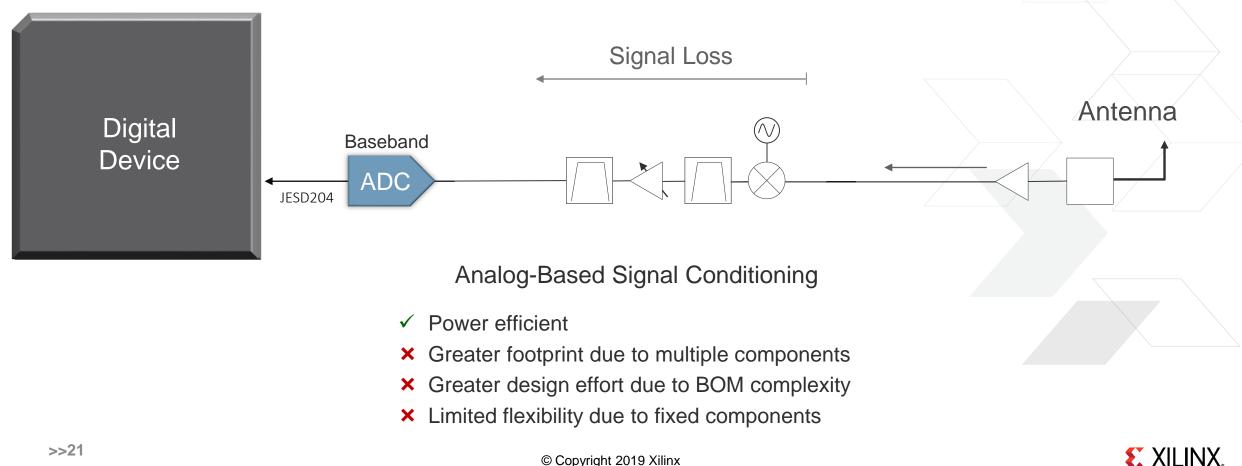

# Platform Flexibility with Direct RF-Sampling

Traditional IF (Intermediate Frequency) Sampling Signal conditioning **before** ADC sampling using **analog** components

© Copyright 2019 Xilinx

# **Platform Flexibility with Direct RF-Sampling**

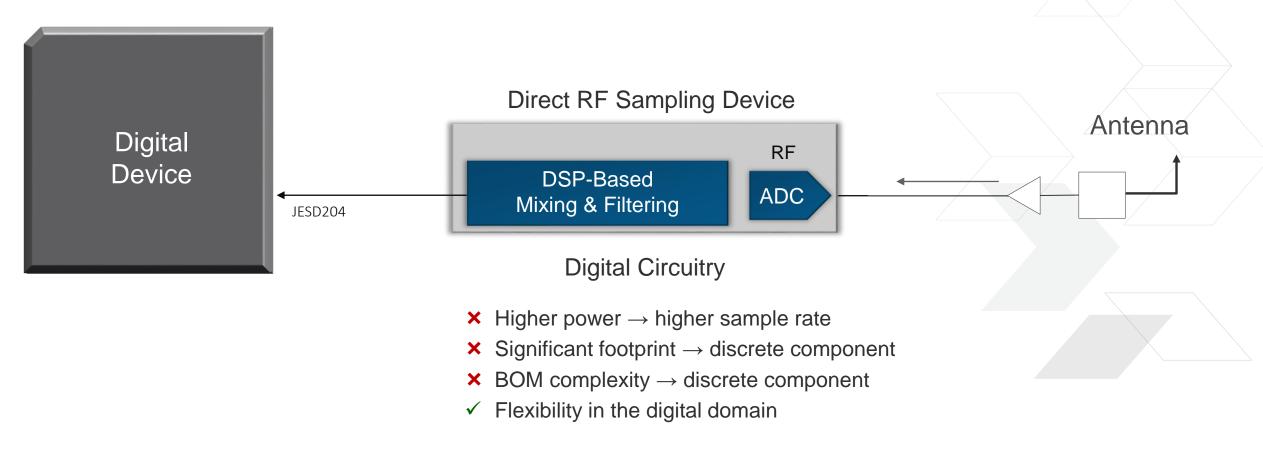

### **Direct RF Sampling**

Signal conditioning after ADC sampling, in the digital domain

**E** XILINX.

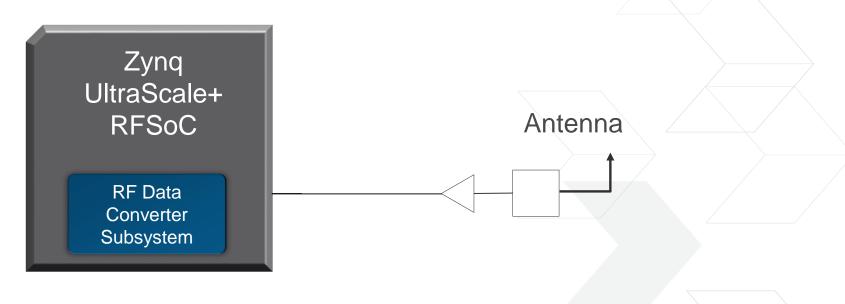

# **Platform Flexibility with Direct RF-Sampling**

### **Direct RF Sampling**

Signal conditioning after ADC sampling, in the digital domain

- ✓ Lower power through integration

- ✓ Smaller footprint through integration

- ✓ Faster design cycle with less BOM complexity

- ✓ Flexibility in the digital domain

### **Scalability Across the Portfolio**

|                           |                                   |                            | -                          | ← Gen 1 |        |                |        | Gen 2 Gen 3 (FDD Support) |                |      |           |                   |                 |             |

|---------------------------|-----------------------------------|----------------------------|----------------------------|---------|--------|----------------|--------|---------------------------|----------------|------|-----------|-------------------|-----------------|-------------|

|                           | [                                 |                            | Radio                      |         | •      | •              | •      | •                         |                |      |           | •                 | •               | •           |

|                           | ľ                                 | Backhaul                   |                            |         |        |                | •      |                           |                |      |           |                   |                 |             |

|                           | ľ                                 | В                          | aseband                    |         |        |                |        |                           |                |      |           |                   |                 |             |

|                           | Ī                                 | Fixed W                    | /ireless Access            |         |        |                | •      |                           | •              |      |           | •                 |                 | •           |

|                           |                                   | Cable R-PHY                |                            |         |        |                | •      |                           |                |      |           |                   | ٠               |             |

|                           |                                   | Satellite / Te             | est & Measurement          |         |        | •              |        | •                         |                |      |           | •                 |                 | •           |

|                           |                                   | Rad                        | ar / SIGINT                |         |        |                |        | ۲                         |                |      |           |                   |                 |             |

|                           |                                   |                            |                            | ZU21DR  | ZU25DR | ZU27DR         | ZU28DR | ZU29DR                    | ZU39DR         | ZU4  | 6DR       | ZU47DR            | ZU48DR          | ZU49DR      |

|                           |                                   | RF-ADC<br>w/DDC            | # of ADCs                  | -       | 8      | 8              | 8      | 16                        | 16             | 8    | 4         | 8                 | 8               | 16          |

|                           |                                   |                            | Max ADC rate (GSPS)        | -       | 4.096  | 4.096          | 4.096  | 2.058                     | 2.275          | 2.5  | 5.0       | 5.0               | 5.0             | 2.5         |

| c                         |                                   |                            | Resolution (bits)          | -       | 12     | 12             | 12     | 12                        | 12             | 14   | 14        | 14                | 14              | 14          |

| RI RI                     | RF Data<br>Converter<br>Subsystem | RF-DAC<br>w/DUC            | # of DACs                  | -       | 8      | 8              | 8      | 16                        | 16             | 12   |           | 8                 | 8               | 16          |

|                           |                                   |                            | Max DAC Rate (GSPS)        | -       | 6.554  | 6.554          | 6.554  | 6.554                     | 6.554          | 10.0 |           | 10.0              | 10.0            | 10.0        |

| Signal Chain<br>Co<br>Snr |                                   |                            | Resolution (bits)          | -       | 14     | 14             | 14     | 14                        | 14             | 1    | 4         | 14                | 14              | 14          |

|                           |                                   | SD-FEC                     |                            | 8       | -      | -              | 8      | l -                       | -              | 8    | 3         | -                 | 8               | -           |

|                           |                                   | RF input Freq max. GHz     |                            |         |        | 4              |        |                           | 5              |      |           | 6                 |                 |             |

|                           |                                   | Decimation / Interpolation |                            |         |        | 1x, 2x, 4x, 8x |        |                           | 1x, 2x, 4x, 8x | 1x,  | 2x, 3x, 4 | x, 5x, 6x, 8x, 10 | x, 12x, 16x, 20 | x, 24x, 40x |

| Logic (PL)                |                                   |                            | System Logic Cells (K)     | 930     | 678    | 930            | 930    | 930                       | 930            | 93   | 30        | 930               | 930             | 930         |

|                           | tograted                          | DSP Slices                 |                            | 4,272   | 3,145  | 4,272          | 4,272  | 4,272                     | 4,272          | 4,2  | 72        | 4,272             | 4,272           | 4,272       |

|                           | Integrated<br>IP                  | GTY Transceivers           |                            | 16      | 8      | 16             | 16     | 16                        | 16             | 1    | 6         | 16                | 16              | 16          |

| Ĩ                         |                                   |                            | PCle <sup>®</sup> Gen 3x16 | 2       | 1      | 2              | 2      | 2                         | 2              | ź    | 2         | 2                 | 2               | 2           |

|                           |                                   | 100G Ethernet w/RS-FEC     |                            | 2       | 1      | 2              | 2      | 2                         | 2              | 2    | 2         | 2                 | 2               | 2           |

|                           | D1156                             | 35x35                      |                            |         |        |                |        |                           |                |      |           |                   |                 |             |

| 5                         | E1156                             | 35x35                      |                            |         |        |                |        |                           |                |      |           |                   |                 |             |

| d d                       | G1517                             | 40x40                      |                            |         |        |                |        | l                         |                |      |           |                   |                 | 1           |

| 운 F                       | F1760                             | 42.5x42.5                  |                            |         | I      | I              |        |                           |                |      |           |                   |                 |             |

| H                         | H1760                             | 4                          | l2.5x42.5                  |         | I      | 1              |        | 1                         |                |      |           |                   |                 |             |

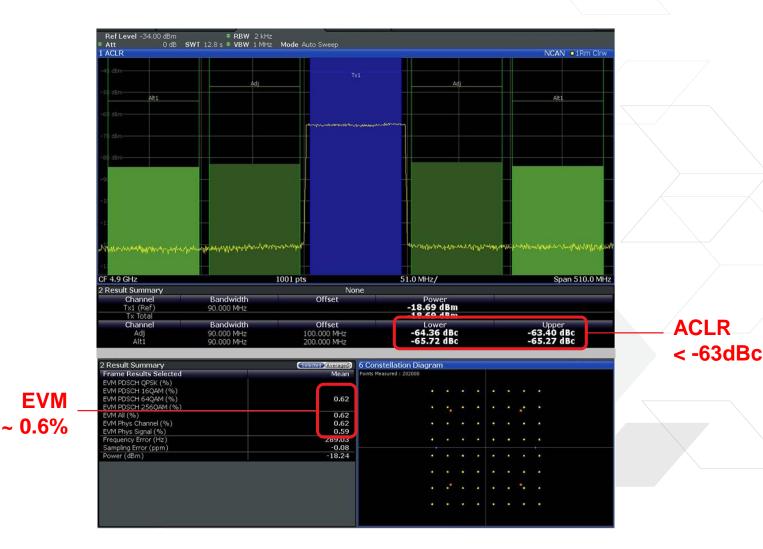

### Zynq UltraScale+ RFSoC Results for the Latest 5G Bands ZU39DR supporting 5G NR band n79 with Direct RF

#### > 5G NR n79 F<sub>OUT</sub> = 4.9GHz

- >> 100MHz 64QAM waveform

- Internal PLL

- >> DAC mode = 32mA

- >> SCS = 30KHz

- $\rightarrow$  F<sub>S</sub> = 5.898GSPS

- >> Internal PLL F<sub>REF</sub> = 491.52MHz

- >> DAC in 32mA mode

#### > Measured Results

- $\rightarrow$  F<sub>OUT</sub> = 4.9GHz

- >> ADJ / ALT Channel < –63dBc

- >> EVM ~0.6%