Zynq UltraScale+ MPSoC

Heterogeneous multiprocessing platform for a broad range of embedded applications.

Enabling faster response times and greater reliability for life-saving defibrillators

Automated External Defibrillators (AEDs) are similar to electrocardiograms (ECG) or multi-parameter patient monitors, and also provide life-saving therapy. ECGs monitor heart signals via electrodes connected to specific locations on the human body. These signals, on the order of a few millivolts in amplitude, are difficult to discern against a noisy background, but are used to accurately determine a person’s QRS complex. The QRS complex is what is commonly used by doctors to diagnose a wide range of heart conditions, such as arrhythmia or atrial or ventricular fibrillation. The AED uses the same QRS complex to make the decision to provide therapy, or the shock to resynchronize the heart.

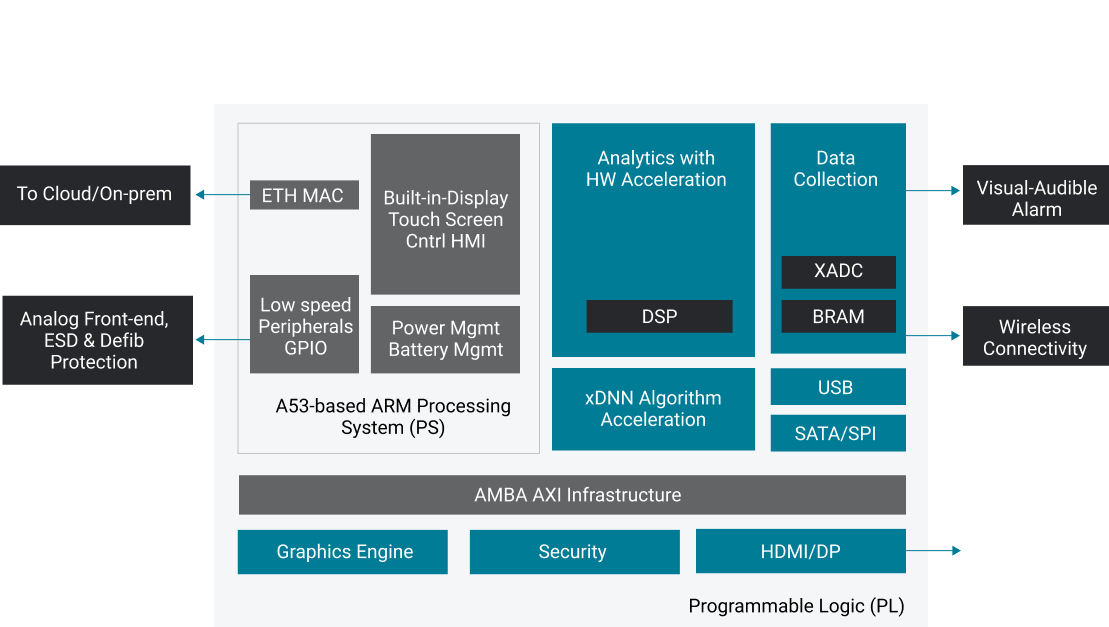

Reliability, easy-to-use HMI, accuracy, fast boot times, power management, and security are just some of the key considerations for AEDs. These systems need processing power that is powerful enough to acquire, process, and interpret several parameters at once, while also providing a straightforward HMI. A simplified architecture of a typical AED can have a built-in SVGA resolution display, a touch screen HMI, and separate external display connectivity to a high-definition monitor (to provide or maybe to show a related video). Modern AEDs are networked with wired and wireless connectivity.

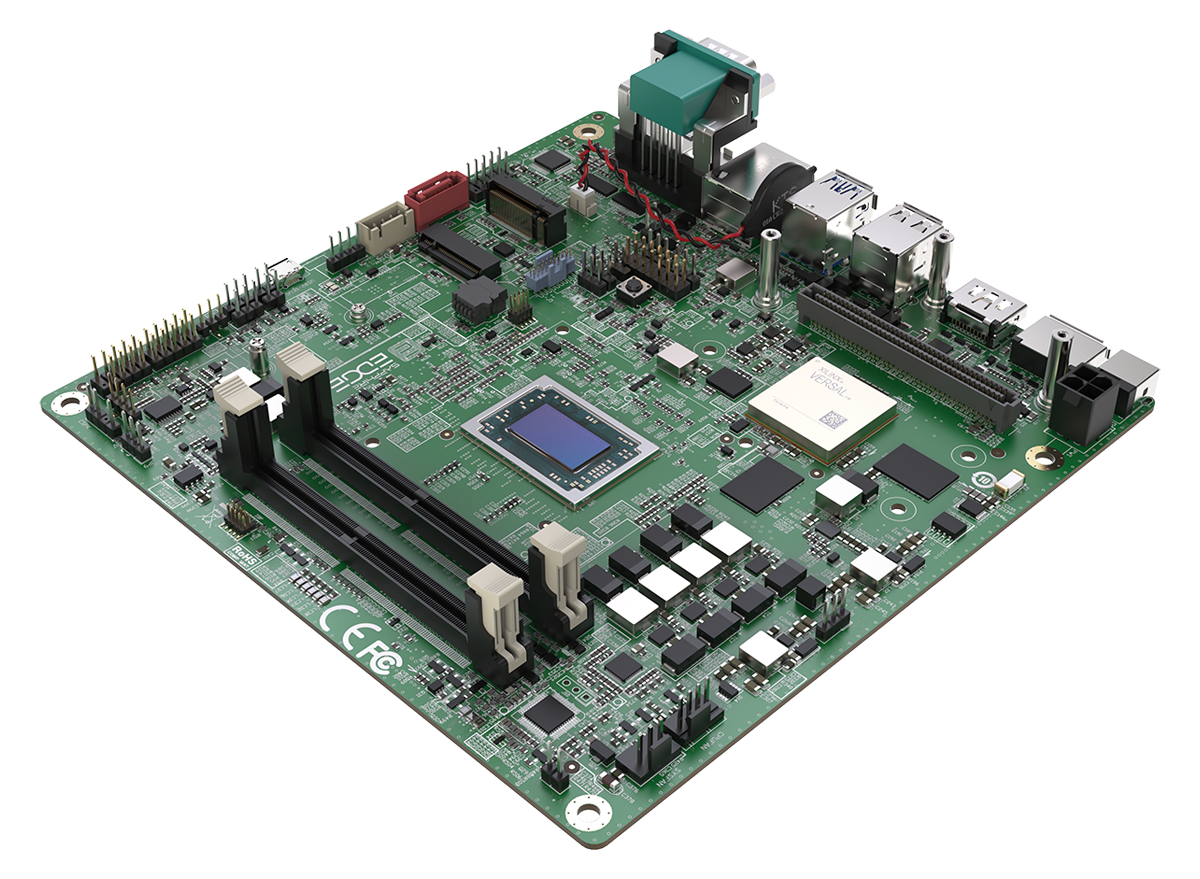

A high-level block diagram is shown here of a smart, connected, high performance, low power AED device. It includes a single, dual, or quad core AMD Zynq™ Ultrascale+™ MPSOC with an optimally configured FPGA fabric, depending on the performance-per-watt and price/cost trade-off requirements. The new ZU1 MPSoC, along with the rest of the Zynq Ultrascale+ family of products, provides the scalability to create low to high-end AED devices using the same software footprint, at low power and cost. The customer could also choose to design with AMD Kria™ SOMs for faster time-to-market.

Defibrillators can be smart and connected to the network in the back end. A smart Defib/Monitor (like a patient-vest) would have the capability to send secure data to the cloud (Hybrid or Private) for analytics and storage. It will also be able to support local and networked high-definition displays.

The processing systems in Zynq UltraScale+ adaptive SoC devices are very powerful. A complex architecture could support using a hypervisor with guest OS versions running Linux for a variety of tasks like control plane, monitoring, diagnostics, and analytics. Many supported commercial RTOS (QNX Neutrino, VxWorks, or ThreadX) or open-source RTOS (Micrium or SafeRTOS) can be used for real-time tasks.

E-Book Offer

New advances in technology are helping revolutionize the healthcare landscape. Download the eBook to uncover key industry challenges and learn how technology creates new ways to treat and diagnose diseases, power research, and enable doctors to perform surgeries with greater precision.

Find medical boards and kits powered by AMD.

Contact an AMD Sales representative.