Adaptive SoCs for Any Application

AMD Versal™ adaptive SoCs integrate capabilities that far exceed those of conventional CPUs, GPUs, and FPGAs, enabling adaptive, domain-specific architectures to accelerate whole applications.

Unmatched Performance and Power

This white paper provides an analysis of Versal adaptive SoC system-level capabilities for a host of markets ranging from edge and cloud to wired networking and 5G/6G wireless infrastructure.

Learn how the Versal architecture delivers world-class performance/watt leadership over competing 10 nm FPGA architectures in end-applications such as AI inference, Massive MIMO, network acceleration, storage, and multi-terabit SmartPHY—supported with data that can be validated with public tools.

AMD Versal adaptive SoCs enable a new paradigm of system design while building on proven FPGA design methodologies. The Versal architecture is a fully software-programmable, heterogeneous compute architecture with a breadth of hard IPs.

This portfolio includes both general-purpose adaptive SoCs and devices with specialized capabilities such as AI Engines for DSP and machine learning workloads, integrated RF-ADCs/RF-DACs, expanded DSP hard IP, or high-bandwidth memory.

The built-in silicon features coupled with a streamlined design flow and the latest enhancements in Vivado™ tools enable both automation and user control to achieve breakthrough system performance per watt.

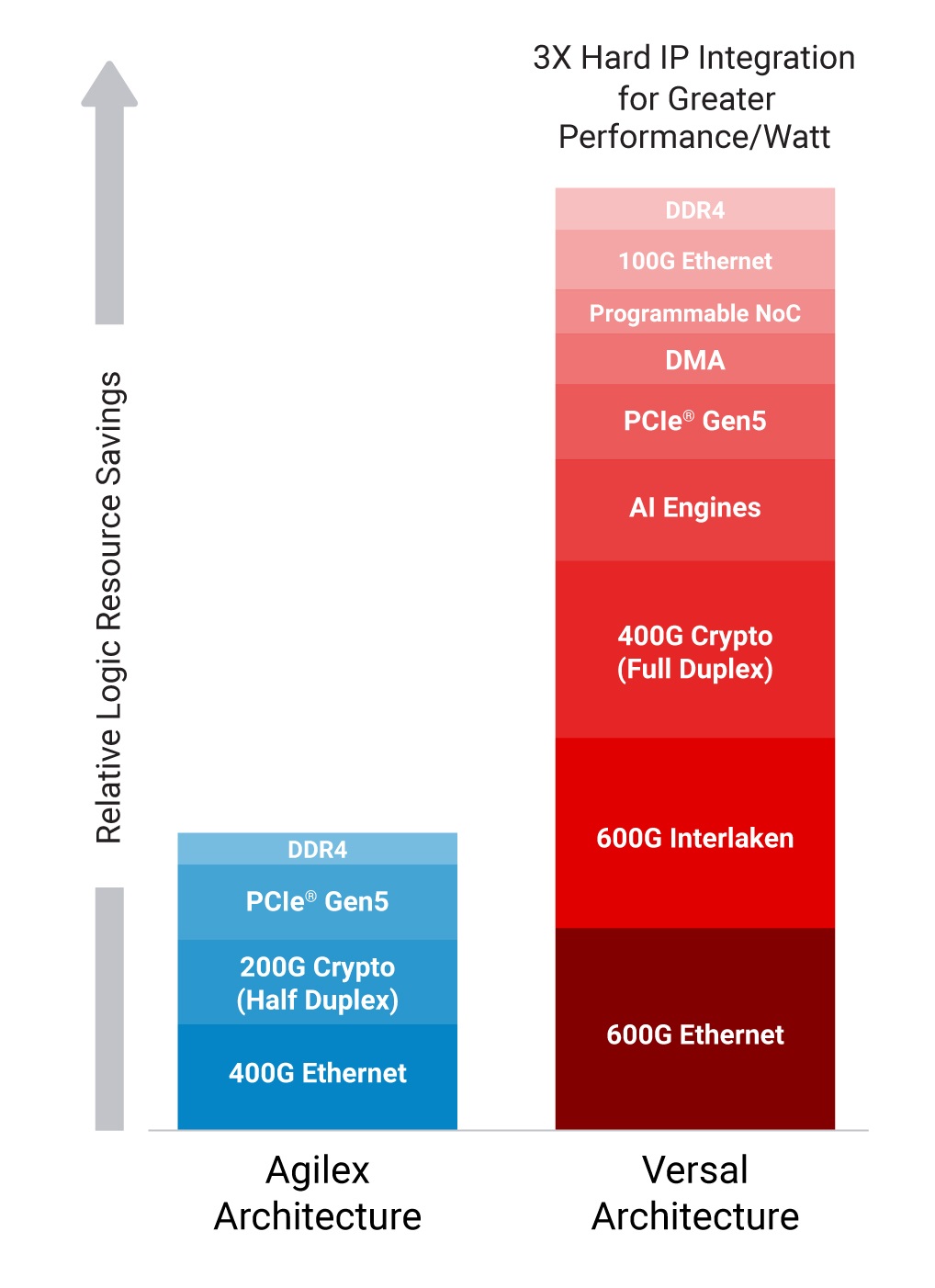

With 3X more hard IP than competing 10 nm FPGAs, Versal adaptive SoCs feature common infrastructure, such as the programmable NoC, across all devices for ease of programming and code portability as well as domain-specific hard IP for diverse markets.

The balance of programmable logic and hard IP delivers performance/watt leadership for advanced applications in cloud, network, and edge, all while retaining hardware flexibility to adapt to changing requirements and market dynamics.

Verify AMD Versal Benchmarks vs. Competing FPGAs as Cited in White Paper WP539

*Registration requests will be qualified

Join the Versal portfolio notification list and be the first to receive updates.